# Instruction Manual

# Bedienungsanleitung

Hardware-Beschreibung

für Kontron PSI80/82-Systeme

KONTRON KONTRON KONTRON KONTRONIK GRUPPE KONTRONIK GRUPPE KONTRONIK GRUPPE KONTRON

# Kontron PSI80/82

# Hardware-Beschreibung

Version: 5.3

Stand: 1. Dezember 1982

Das vorliegende Handbuch beschreibt Aufbau und Funktion der Hardware in den Computersystemen der Kontron PSI80/82-Serie. Die darin enthaltene Information ist für den Anwender vor allem in folgenden Fällen wesentlich:

- \* Anschluß nicht standardmäßiger Peripherie

- \* Nachrüsten von zusätzlichen PROM-residenten Programmen (z.B. für Diagnose-Zwecke)

- Erweiterung des Geräts um optionale Hardware (z.B. ECB-Zusatzkarten)

- \* Erstellung von ASSEMBLER-Software, die direkten Zugriff auf Hardwaregegeben eiten nimmt (z.B. spezielle Ein-/Ausgabe-Treiber, Echtzeitaufgaben, Memory Mapping usw.).

Für andere, nicht hardwarespezifische Aufgaben ist die Verwendung des Kontron PSI-Bedienungshandbuchs voll ausreichend.

# INHALTSVERZEICHNIS

| 1.                                                                        | Übersicht                                                                                                                                                                                                                                                      |

|---------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.                                                                        | Architektur der Rechnerbaugruppe                                                                                                                                                                                                                               |

| 3.1.3.1.1<br>3.1.2<br>3.1.2.1<br>3.1.2.2<br>3.1.2.2<br>3.1.2.3<br>3.1.2.4 | Hardwarebeschreibung Zentraler Rechnerteil Zentraleinheit Speicherbereiche Festwertspeicher Schreib-/Lesespeicher (System RAM) Bildwiederholspeicher (Video RAM) Externe Speicher                                                                              |

| 3.2.6                                                                     | Ein-/Ausgabekanäle Ein-/Ausgabebausteine Statusport Tastaturanschluß Serienschnittstellen Parallelschnittstelle Zähler-/Zeitgeber-Kanäle Floppy Disk Controller und Floppy Disk Laufwerke Video Controller Interrupt-Priorität Lautsprecher- und Resetanschluß |

| 4.<br>4.1<br>4.2<br>4.3<br>4.4                                            | Zusatzbaugruppen CPU/DMA-Adapter RS 422/423-Option Modem-Option Softwareschutz PROM                                                                                                                                                                            |

| 5.<br>5.1<br>5.2<br>5.3<br>5.4                                            | Beschreibung des Einschubrahmens<br>ECB-Bus Standard<br>Adressierung im ECB-Bus<br>Interruptsteuerung im Einschubrahmen<br>Stromversorgung des Einschubrahmens                                                                                                 |

| 6.                                                                        | Netzteil                                                                                                                                                                                                                                                       |

| 7.1<br>7.1<br>7.2<br>7.3<br>7.4<br>7.5                                    | Festplattenanschluß Funktionseinheiten Schaltungsbeschreibung Disk I/O-Prozessor MSC 9056 ST506-Laufwerk Interface ECB/DS - Anschluß                                                                                                                           |

1 1 1

1 1 t t 1 1 1

PSI80-Hardware Übersicht

# 1. Übersicht

Diese technische Beschreibung der zentralen Hardware der Computersysteme der Serien Kontron PSI80 und PSI82 gilt der Architektur, den Funktionen und den Ausbaumöglichkeiten eines modernen leistungsfähigen Kompaktcomputers.

Es wird von Fall zu Fall auf Schalt- und Bestückungspläne verwiesen, die zum Lieferumfang eines jeden Systems gehören. Außerdem werden Datenblätter und Beschreibungen folgender großintegrierter Schaltkreise verwendet:

ZILOG - Z80 A-CPU\* ZILOG - Z80 A-SIO\* ZILOG - Z80 A-PIO\* ZILOG - Z80 A-CTC\* NEC - uPD765 MOTOROLA - MC6845

Diese Bauteile werden im Text zumindest kurz charakterisiert. Im allgemeinen ist eine direkte Programmierung dieser Komponenten nicht notwendig, da sie durch die Betriebs-Software bereits entsprechend ihrer Verwendung im PSI80-System initialisiert sind.

Die Datenblätter dieser Bausteine gehören nicht zum Lieferumfang und sind im Bedarfsfall direkt vom Lieferanten zu beziehen (im Falle der Z&-Bausteine von Kontron).

Die Kontron PSI80/82-Hardware ist auf einer zentralen Platine aufgebaut. Unterschiedliche Ausbaustufen sind im allgemeinen mit unterschiedlicher Bestückung verbunden. Außerdem können Unterschiede in der Auslegung und Anzahl der peripheren Einheiten mit den unterschiedlichen Versionen verbunden sein. Es wird, soweit erforderlich, in der Beschreibung auf diese Varianten Rücksicht genommen.

Maßgeblich ist in jedem Fall die gültige Produkt-Spezifikation.

Kontron PSI80-Systeme sind vom FTZ geprüft:

Zulassungsnummer: C-089/80

Funkentstörgrad: N nach VDE 0875 Modemzulassung: FTZ 02013D PSI80

# 2. Architektur der Rechnerbaugruppe

Basis der Kontron PSI80/82-Computerserie ist die hochintegrierte Computerbaugruppe KDT5 (kleine Datentechnik, Revision 5.3, die eine vollständige Zentraleinheit mit weitreichendem Ausbau umfaßt. Auf dieser Platine sind in der maximalen Ausbaustufe möglich:

- Z80 A-CPU\* Zentral prozessor,

- Programm- und Datenspeicher (max. 16 kByte PROM, 64 kByte RAM),

- Bildschirmprozessor mit 16 kByte Bildwiederholspeicher,

- Tastaturanschluß,

- Controller für 2 ins Gehäuse integrierte Floppy-Disk-Laufwerke,

- Parallel- und Serien-Ein-/Ausgabe sowie eine

- ECB-Busschnittstelle.

Zusätzliche Ausbaumöglichkeiten bietet ein in der Reihe PSI80x/Mx verfügbarer Einschubrahmen für anwendungsorientierte Baugruppen im Kontron ECB-Bus-Standard, die Ein-/Ausgabe-bezogen sein können (Z80A-ECB/AE16, Z80A-ECB/O, ...), Funktionserweiterungen darstellen (Z80A-ECB/A), Speichererweiterungen bieten (Z80A-ECB/D32), oder als autonome Subsysteme arbeiten können.

Die Architektur des Rechners entspricht langjähriger Erfahrung auf dem Gebiet der Schaltungsentwicklung von Mikrocomputersystemen. Die Einheiten auf der Grundplatine wurden nach funktionalen, logischen und elektrischen Gesichtspunkten so angeordnet, daß höchste Betriebssicherheit gewährleistet wird. So wurde beispielsweise strikt darauf geachtet, die Busstruktur des Prozessors (Adreß-/Datenbus) auch im Layout aufrechtzuerhalten, um Störeinflüsse wie Übersprechen etc. von vornherein zu minimieren.

Die Aufteilung in einen 'inneren' und 'äußeren' Datenbus begrenzt die kapazitive Belastung in den einzelnen Bereichen und erhäht samit wiederum die Betriebssicherheit. Der 'innere' Datenbus verbindet alle Z80A-Peripheriebausteine und die Ausgänge der Speicher mit der CPU. Störsichere Schmitt-Trigger-Puffer trennen diesen vom 'äußeren' Datenbus, der alle übrigen Peripherieeinheiten und die Eingänge der Schreib-/Lesespeicher bedient. Diese Anordnung erübrigt einerseits Aufwand zur Bussteuerung für Z80A-E/A-Bausteine und ermöglicht andererseits die Verwendung von Speichern mit einer Zugriffszeit nahe der theoretisch oberen Grenze von 375 ns.

Von diesen beiden Bussystemen elektrisch durch störsichere Schmitt-Trigger-Puffer getrennt ist der 'externe Erweiterungsbus' im ECB-Standard (Reihe "Mx").

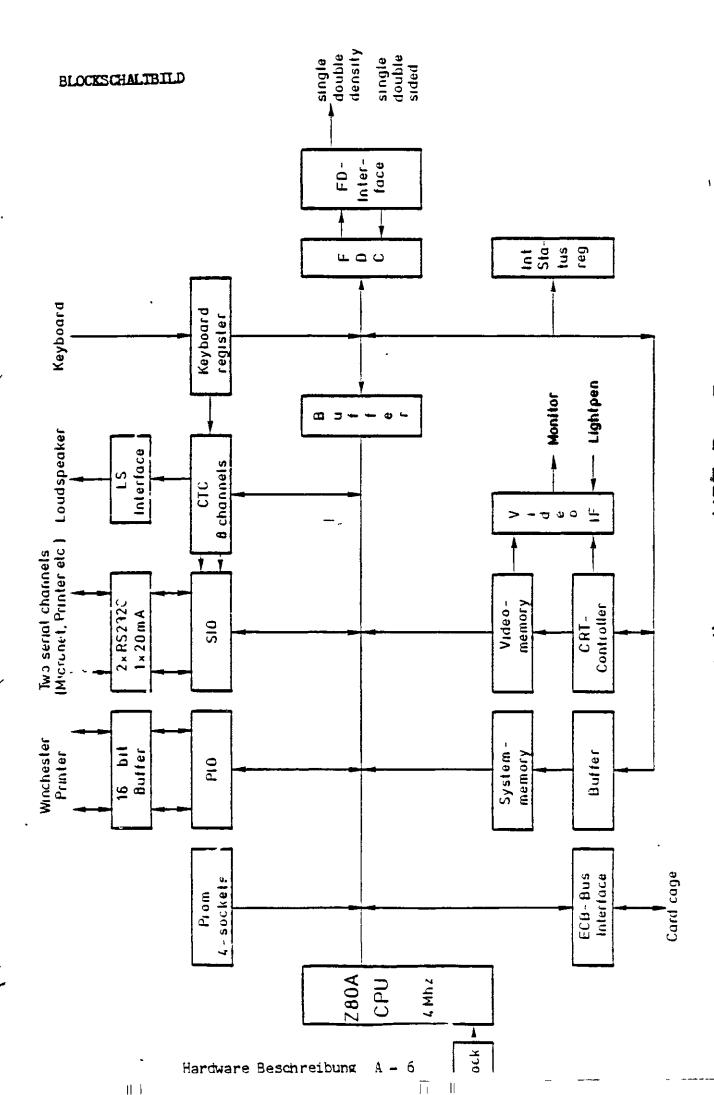

Die folgende Seite zeigt das Blockschaltbild der zentralen Rechnerbaugruppe.

\* Trademarks of ZILOG Inc., Cupertino/CA

Blockdiagram KDT Rev.5

# 3. Hardwarebeschreibung

# 3.1 Zentraler Rechnerteil

Der Rechnerteil ist aus folgenden funktionalen Blöcken aufgebaut:

- CPU mit Buspuffern

- Festwertspeicher

- Schreib-/Lesespeicher

- Ein-/Ausgabeschnittstellen

- Bildprozessor mit Bildwiederholspeicher

- Floppy Disk-Prozessor \*

Die folgenden Abschnitte beschreiben Einzelheiten der Baugruppe.

\* nicht bei Kontron PSI80/IC, PSI80/MO

### 3.1.1 Zentraleinheit

Die CPU besitzt drei verschiedene Bussysteme: Adreß-, Steuer- und Datenbus. Die beiden erstgenannten sind unidirektional, d.h. sie gehen immer von der CPU aus und führen von dort im Prinzip zu allen auf der Baugruppe vorhandenen Funktionsgruppen.

Der Datenbus ist bidirektional, d.h. der Informationsstrom kann sowohl von außen zur CPU (Lesevorgang), als auch umgekehrt (Schreibvorgang) fließen. Zur Steuerung der entsprechenden Richtung und um zu verhindern, daß mehrere Datenquellen gleichzeitig den Bus beanspruchen, ist eine Bussteuerung vorhanden.

Die PSI80-/entralbaugruppe hat einen zweigeteilten Datenbus. Der 'innere Datenbus' (1D0...ID7) verbindet alle Z80 A-Peripheriebausteine, den PROM-Bereich und die Ausgänge sämtlicher Speichereinheiten mit der CPU. Der 'äußere Datenbus' (AD0...AD7) schließlich bedient die Eingänge der Schrei -/Lesespeicher und die übrigen Peripheriecinheiten

In den Reihen 'Mx' der PSI80-Computerkarte steht für Erweiterungen mit ECB-Baugruppen auch ein externer Erweiterungsbus zur Verfügung. Dieser ist über einen eigenen bidirektionalen Puffer mit dem 'inneren' Datenbus verbunden. Der externe Adreß- und Steuerbus ist identisch mit dem internen. Für Erweiterungen steht ein FAN-OUT von etwa 7 TTL-Lasten zur Verfügung (ca. 30 LS TTL-Lasten).

# 3.1.2 Speicherbereiche

Auf der PSI80-Zentralbaugruppe sind 3 verschiedene Speicherbereiche, sowie die Steuerlogik für einen weiteren externen Speicherbereich (über ECB- oder S100-Bus) mit bis zu sechs Speicherbänken vorhanden.

|                        | Bezeichnung                                        | Kapazität                | Speichertyp               |

|------------------------|----------------------------------------------------|--------------------------|---------------------------|

| 1.                     | Festwertspeicher                                   | max. 16 kByte            | EProm (5V Versorgung)     |

| <ol> <li>3.</li> </ol> | System Schreib-/<br>Lesespeicher<br>Bildwiederhol- | 64 kByte                 | RAM dynamisch             |

| 4.                     | speicher<br>externer Speicher                      | 16 kByte<br>max. 1 MByte | RAM dynamisch<br>beliebig |

Zur Auswahl der einzelnen Bereiche stehen über einen Statusport drei Steuersignale zur Verfügung. Folgende Adresbereiche sind belegt (gültig für Prom P7-Standardprogrammierung):

| POFF | MAP1 | MAPO | J6                   | PROM             | SYSRAM                                 | VID.RAM        | Ext.RAM                |

|------|------|------|----------------------|------------------|----------------------------------------|----------------|------------------------|

| 0    | 0    | 0    | ein<br>aus           | 0-1FFF<br>0-3FFF | 2000-FFFF<br>4000-FFFF                 | •              | -                      |

| 0    | 0    | 1    | ein                  | 0-3FFF<br>0-1FFF | 2000-7FFF<br>C000-FFFF                 | 8000-BFFF      | -                      |

|      |      |      | aus                  | 0-3FFF           | 4000-7FFF<br>000-FFFF                  | 8000-BFFF      | -                      |

| 0    | 1    | 0    | ein<br>aus           | 0-1FFF<br>0-3FFF | 2000-3FFF                              | ,              | 4000-BFFF              |

| 0    | 1    | 1    | x<br>ein<br>aus<br>x | 0-1FFF<br>0-3FFF | 000-FFFF<br>2000-3FFF<br>-<br>000-FFFF | 8000-BFFF      | 4000-7FFF              |

| 1    | 0    | 0    | x                    |                  | 0000-FFFF                              |                | -                      |

| 1    | 0    | 1    | X                    | -                | 0000-7FFF<br>000-FFFF                  | 8000-BFFF      | •                      |

| 1    | 1    | 0    | x<br>x               | <del>-</del>     | 0000-3FFF<br>0000-3FFF                 | -<br>8000-BFFF | 4000-BFFF<br>4000-7FFF |

Speicheradresbereiche (x --> beliebig)

Das Verfahren zur Programmierung des Statusports ist im Abschnitt 3.2.2 beschrieben.

1 1 1 . . **[**]

# 3.1.2.1 Festwertspeicher

Die Baugruppe enthält vier Steckplätze für folgende EProm-Typen mit 5Volt Versorgungsspannung:

|                  | J6     |        |

|------------------|--------|--------|

| i2716<br>TMS2532 | A<br>B | A<br>B |

|                  |        |        |

Der Adreßbereich reicht in Abhängigkeit von Jumper J6 von 0-1FFFH (8 kByte) bzw. von 0-3FFFH (16 kByte) und ist als 'Nur-Lesespeicher' realisiert. Der Systemspeicher (RAM) im selben Adreßbereich ist als 'Nur-Schreibbereich' zugänglich, während der Festwertspeicher selektiert ist.

Standardmäßig sind drei Promplätze bestückt: 4 KByte für ein Monitorprogramm für Servicezwecke und 2 KByte als BOOT-PROM zum Laden des Betriebssystems von Diskette, Festplatte oder Bubble-Speicher.

# 3.1.2.2 Schreib-/Lesespeicher (System RAM)

Dieser Bereich umfaßt 64 kByte (4 Bänke je 16 kByte) und ist mit dynamischen RAMs (16 kBit x 1) realisiert. In Abhängigkeit der Statusleitungen POFF, MAP1 und MAFO stehen unterschiedliche Adreßbereiche als System RAM zur Verfügung.

# 3.1.2.3 Bildwiederholspeicher

Dieser Bereich umfaßt 16 kByte und ist ebenfalls mit 16k x 1 Bit dynamischen RAMs realisiert. Der Adreßbereich liegt zwischen 8000H und BFFFH, falls das Bit MAFO den Wert 1 hat.

Der Bildwiederholspeicher ist für CPU-Zugriffe transparent. Dies bedeutet, daß Bildprozessor (CRTC 6845) und CPU virtuell gleichzeitig auf diesen Speicherbereich zugreifen können. Zugriffe auf den Bildwiederholspeicher erfordern das entsprechende Setzen der Statusleitung MAPO (siehe Abschnitt 3.2.2).

# 3.1.2.4 Externer Speicher (1)

Über den ECB-Bus können von der Adreßauswahl her bis zu 6 zusätzliche Speicherbänke angeschlossen werden. Zu diesem Zweck werden auf der zentralen Baugruppe 6 verschiedene MBS-Signale (Memory bank select) erzeugt und auf den ECB-Bus geführt.

Externe Speicherbaugruppen müssen eines dieser Signale (MBSO bis MBS5) als Card select-Signal verwenden. Der Adreßbereich externer Speicher hängt ab von den Statusleitungen MAFO und MAP1.

Die Kapazität einer einzelnen externen Speicherbaugruppe darf bis zu 32 kByte betragen. Dies entspricht der Standardprogrammierung von Prom 7 (HM 7603).

Busbelegung der MBS-Signale: (2)

| MBS0 | ECB | BUS: | 10 c |

|------|-----|------|------|

| MBS1 |     |      | 12c  |

| MBS2 |     |      | 13c  |

| MBS3 |     |      | 14a  |

| MBS4 |     |      | 23c  |

| MBS5 |     |      | 19c  |

|      |     |      |      |

Diese Signale sind nur dann aktiv, wenn tatsächlich ein Zugriff auf einen externen Speicherbereich stattfindet. Welches der 6 MBS-Signale in einem solchen Fall aktiv wird, hängt vom Inhalt des Mapper Ports (IC13: 74LS137) ab. Dieser kann durch Port-Write Befehle (Adresse: 1AH) entsprechend gesetzt werden.

| D7D3 | D2 | D1 | $\infty$ | Signal |

|------|----|----|----------|--------|

| X    | 0  | 0  | o        | MBS0   |

| X    | 0  | 0  | 1        | MBS1   |

| X    | 0  | 1  | 0        | MBS2   |

| x    | 0  | 1  | 1        | MBS3   |

| X    | 1  | 0  | 0        | MBS4   |

| X    | 1  | 0  | 1        | MBS5   |

| X    | 1  | 1  | 0        | MBS6   |

|      |    |    |          |        |

# x ---> beliebig

- (1) nur bei PSI80x/Mx-Serie

- (2) Diese Signale sind bei PSI80-Systemen in der eingebauten Busplatine verdrahtet (siehe Abschnitt: Einschubrahmen). Die Verdrahtung des Card-Select-Signals der 'externen' Speicherkarte auf die gewünschte MBS-Leitung ist Anwender-seitig vorzunehmen.

# 3.2 Ein-/Ausgabekanäle

# 3.2.1 Ein-/Ausgabebausteine

Die Baugruppe enthält folgende E/A-Bausteine (1):

| Adresse (hex)        | Baustein                                  | Port                                                           | implementiert bei                                |

|----------------------|-------------------------------------------|----------------------------------------------------------------|--------------------------------------------------|

| 00<br>01<br>02<br>03 | Z80 A-DMA<br>AM 2918<br>-                 | DMA-Port<br>Control Register                                   | ) DMA-<br>) Option                               |

| 04<br>05<br>06<br>07 | Z80A—SIO/O(/9) " " "                      | Port A-Data<br>Port B-Data<br>Port A-Control<br>Port B-Control | ) PSI80(D)/xx<br>) (1)<br>) PSI80(D)/xx<br>) (1) |

| 08<br>09<br>0A<br>0B | Z80 A_CTC_1                               | Kanal O<br>Kanal 1<br>Kanal 2<br>Kanal 3                       | )<br>) PSI80(D)/xx<br>)                          |

| OC<br>OD<br>OE<br>OF | Z 80 A-PIO                                | Port A-Data Port B-Data Port A-Control Port B-Control          | )<br>) PSI80(D)/Mx<br>)                          |

| 10<br>11<br>12<br>13 | Z80 A_CTC-2                               | Kanal O<br>Kanal 1<br>Kanal 2<br>Kanal 3                       | )<br>) PSI80(D)/xx<br>)                          |

| 14<br>15<br>16<br>17 | FDC 765                                   | Main Status Reg.<br>Data Reg.                                  | ) PSI80(D)/M2, M1<br>)<br>) PSI80(D)/S2, S1      |

| 18<br>19             | CRTC-6845                                 | Adreßregister<br>Registerfile                                  | ) PSI80(D)/xx<br>)                               |

| 1A<br>1B             | IC13 : Mapper<br>Prom5 : Softwa<br>PROM S | re protection                                                  | ) PSI8O(D)/Mx<br>) optional                      |

| 1C<br>1D             | IC40 : Status                             | port Strobe<br>rd Input Port Strob                             | ) PSI80(D)/xx<br>e ) PSI80(D)/xx                 |

| 1E<br>1F             |                                           | Data Acknowledge)<br>Terminal Count)                           | ) PSI80(D)/M2,M1,<br>) S2, S1                    |

<sup>(1)</sup> zur Beachtung: nicht bei allen Kontron PSI-Versionen implementiert (siehe Produktspezifikation)

# 3.2.2 Statusport

Über den Statusport (Baustein IC40: 74LS273) werden alle Steuerleitungen der Baugruppe bedient. Der Statusport ist über die I/O-Adresse 1CH erreichbar.

# Achtung:

Dieser Port kann und darf nicht gelesen werden. Der momentane Inhalt des Statusports ist im Betriebssystem KOS in der Speicherstelle 3 abgelegt. Ändern des Statusports durch Anwenderprogramme nur unter Interruptsperre. Gleichen Inhalt in Port und Speicherstelle 3 schreiben! Interruptroutinen des Betriebssystems beeinflussen ebenfalls beide Inhalte.

# Bitzuordnung:

| STO | _ | MAP O         |

|-----|---|---------------|

| ST1 | - | MAP 1         |

| ST2 | _ | Sound Trigger |

| ST3 | - | Video Invert  |

| ST4 | - | Alpha/Graphik |

| ST5 | - | Prom off      |

| ST6 | - | Standard/Mini |

| ST7 | _ | Motor on      |

Die Funktion der Signale wird in der folgenden Signalbeschreibung dargestellt.

Extern

Video

# Signalbeschreibung:

MAP1

0

MAPO

0

MARO/MAP1 Memory map Signale zur Auswahl interner und externer Speicherbereiche (siehe auch Abschnitt: Speicher)

System

0000-FFFF

|      | 0            | 1 | C000-                        | -7FFF<br>-FFFF                                 | 8000-BFFF                                                                                   |                     |

|------|--------------|---|------------------------------|------------------------------------------------|---------------------------------------------------------------------------------------------|---------------------|

|      | 1            | 0 |                              | -3FFF<br>-FFFF                                 | -                                                                                           | 4000-BFFF           |

|      | 1            | 1 | 0000-                        | -3FFF<br>-FFFF                                 | 8000-BFFF                                                                                   | 4000-7FFF           |

|      |              |   |                              |                                                |                                                                                             |                     |

| ST2: | Sound Trigge | r | triggert ein<br>aktiviert fi | n Monoflo<br>ür die Da<br>rausgang<br>ggerbar. | e auf dieser Le<br>op (IC36: 74LS1<br>ouer von etwa 0<br>'SOUND OUT'. Do<br>Die Frequenz de | 23) und<br>.5 s den |

|      |              |   | von handi o                  | 405 010-                                       | -C G5+                                                                                      |                     |

| ST3: | Video Invert |   | Invertiert                   | den Video                                      | ausgang                                                                                     |                     |

|      |              |   | ST3=1><br>ST3=0>             |                                                | rund dunkel<br>rund hell                                                                    |                     |

| ST4: | Alpha/Graph  |   | Umschaltung<br>graphischer   |                                                | n alphanumerisc<br>sart                                                                     | her und             |

|      |              |   |                              |                                                | che Betriebsart<br>Berische Betrie                                                          |                     |

| ST5; | Prom off     |   | Ein-/Aussch                  | altung de                                      | s Prambereichs                                                                              |                     |

|      |              |   |                              |                                                | eich eingeschal<br>eich ausgeschal                                                          |                     |

| ST6: | STD/Mini     |   | Einstellung<br>Standard- o   | des Disk<br>der Minil                          | controllers au<br>aufwerke                                                                  | f                   |

|      |              |   | ST6=0><br>ST6=1>             |                                                |                                                                                             |                     |

| ST7: | Motor on     |   | 'Motor On'-                  | Leitung f                                      | Tür 5 1/4" Lauf                                                                             | werke               |

|      |              |   | ST7=0><br>ST7=1>             |                                                | ogeschaltet<br>Ingeschaltet                                                                 |                     |

# 3.2.3 Tastaturarschluß

Der Tastaturanschluß erfolgt über ein 8bit TTL-Register (IC44: 74LS374) mit Tristate-Ausgängen. Dieses Register kann als Port (Adresse: 1DH) gelesen werden.

Der Takteingang des Keyboard Input Registers wird durch das Strobe Signal der Tastaturelektronik gesteuert. Dieses geht zur Generierung eines Interrupts gleichzeitig an Kanal 1 von CTC-2. Der Anschluß der Tastaturelektronik erfolgt an Stecker ST-E (26-polig).

| Signalbezeichnung |              | Anschluß ST-E | Pegel     |

|-------------------|--------------|---------------|-----------|

| DATA              | KBO          | E-9           | TTL-input |

| DATA              | KB1          | E-8           |           |

| DATA              | KB2          | E-7           | II        |

| DATA              | KB3          | E-6           |           |

| DATA              | KB4          | E-5           | 11        |

| DATA              | KB5          | E-4           | 11        |

| DATA              | KB6          | E-3           | 11        |

| DATA              | KB7          | E-2           | 11        |

| STROBE            | (invertiert) | E-11          | n         |

| VCC               | +5V          | E-13/26       |           |

| GND               | 0V           | E-1/14        |           |

Belegung von Stecker ST-E (Tastaturanschluß).

ST-E ist 1:1 verdrahtet auf dem untersten 25-poligen Stecker der Rückwand.

# 3.2.4 Serienschnittstellen

Die Baugruppe enthält im Vollausbau zwei unabhängige Serienschnittstellen (Kanal A und B) zum Anschluß beliebiger serieller Sender-/Empfängergeräte (Drucker, Terminals, ECB/C8-Subsysteme etc.). Beide Schnittstellen werden von einem Z80A-SIO/O bedient. Folgende Norm-Schnittstellen sind realisiert:

| KANAL | Adresse | RS232-C | 20mA | RS423    | RS422    |

|-------|---------|---------|------|----------|----------|

|       |         |         |      |          |          |

| A     | 04      | ja      | ja   | optional | optional |

| В     | 05      | ja      | nein | optional | optional |

Sämtliche Signale der beiden Schnittstellen sind auf je einem 25poligen Normstecker herausgeführt (optional 37-polig nach RS 449).

Kanal A ---> ST-F Kanal B ---> ST-G

# Steckerbelegung Kanal A:

| Anschluß SIO                                    | Anschluß ST-F                                                         | Signalbez.                                                                    | Pegel                                                 |

|-------------------------------------------------|-----------------------------------------------------------------------|-------------------------------------------------------------------------------|-------------------------------------------------------|

| TxDA<br>TxDA<br>DTRA<br>RTS A                   | F-3 output F-16 output F-10 outp. return F-5 output F-6 output        | Send data<br>Send data<br>Send data<br>Data terminal ready<br>Request to send | RS232-C<br>20mA (+)<br>20mA (-)<br>RS232-C<br>RS232-C |

| RxDA (J2-A)<br>RxDA (J2-B)<br>-<br>CTSA<br>DCDA | F-2 input<br>F-14 input<br>F-9 inp. return<br>F-4 input<br>F-20 input | Receive data Receive data Receive data Clear to send Data set ready           | RS232-C<br>20mA (+)<br>20mA (-)<br>RS232-C<br>RS232-C |

| TxCA (J3-B)                                     | F-15 input                                                            | Ext. transmitter clock                                                        | RS232-C(*)                                            |

| TxCA (J4-B)                                     | F-17 input<br>F-7<br>F-1                                              | Ext. receiver clock<br>Signal Ground<br>Chassis Ground                        | RS232-C(*) O Volt O Volt                              |

Kanal A ist empfängerseitig standardmäßig für RS232C-Pegel ausgelegt (Jumper J2 in Stellung A). Die Auswahl der 20mA-Schnittstelle erfolgt durch Umstecken vom Jumper J2 auf Stellung B. ST-F ist 1:1 verdrahtet auf dem zweiten (von unten) 25-poligen Stecker der Rückwand.

# Steckerbelegung Kanal B:

| Anschluß SIO  | Anschluß ST-G | Signalbez.          | Pegel     |

|---------------|---------------|---------------------|-----------|

| TxDB          | G-3 output    | Send data           | RS232C    |

| DTRB          | G-5 output    | Data terminal ready | RS232C    |

| RTSB          | G-6 output    | Request to send     | RS232C    |

| RxDB          | G-2 input     | Receive data        | RS232C    |

| CTSB          | G-4 input     | Clear to send       | RS232C    |

| DCDA          | G-20 input    | Data set ready      | RS232C    |

| TxRxCB (J1-B) | G-17 input    | Ext. rec./trans.    | KS232C(*) |

| TxRxCB        | G-24 output   | Int. rec./trans.    | RS232C(*) |

| -             | G-7           | Signal Ground       | O Volt    |

|               | G-1           | Chassis Ground      | O Volt    |

<sup>(\*)</sup> siehe Abschnitt: Einstellung der Baudrate

ST-G ist 1:1 auf dem dritten (von unten) 25-poligen Stecker verdrahtet.

Durch die Option 'Modemschnittstelle' wird Kanal B als Datenendgerät-Schnittstelle mit folgender Belegung implementiert:

Anschluß SIO Anschluß (Rückwand) Signalbezeichnung Norm

| Anschluß SIO | Anschluß (Rückwand) | Signalbezeichnung         | Norm   |

|--------------|---------------------|---------------------------|--------|

| TxDB         | 2                   | Sendedaten                | D1/103 |

| RxDB         | 3                   | Empfangsdaten             | D2/104 |

| DTRB         | 20                  | DE-Einrichtung            | S1/108 |

|              |                     | betriebsbereit            |        |

| RTSB         | 4                   | Sendeteil ein-            | S2/105 |

|              |                     | schalten                  |        |

| -            | 23                  | -                         | -      |

| CTSB         | 6                   | Betriebsbereit-<br>schaft | M1/107 |

| -            | <b>5</b><br>8       | -                         | ~      |

| DCDB         | 8                   | Empfangssignal-           | M5/109 |

|              |                     | pegel                     |        |

| GND          | 7                   | Betriebserde              | E2/102 |

| GND          | 1                   | Schutzerde                | E1/101 |

|              |                     |                           |        |

# Einstellung der Baudraten

Die Baudrate für Kanal A des Z80A-SIO/O wird entweder von Kanal 2 des Z80A-CTC-1 oder, bei synchronen Übertragungsverfahren von einem extern zugeführten Takt bestimmt. Die Wahl zwischen internem und externem Takt erfolgt mit den Jumpern J3 und J4.

| TxCA   | RxCA   | J3 | J4 |

|--------|--------|----|----|

| intern | intern | A  | A  |

| extern | intern | В  | A  |

| intern | extern | A  | B  |

| extern | extern | В  | В  |

Wird interner Takt verwendet, so ist für Kanal 2 von CTC-1 untenstehende Programmiertabelle maßgebend.

Kanal B des SIO-Bausteins erhält den Übertragungstakt entweder von Kanal 1 des CTC-1 (siehe Tabelle), oder von extern für synchrone Anwendungen. Bei Kanal B sind Sender- und Empfängertakt auf dem SIC-Baustein zusammengefaßt.

| TxRxCB | J1 |

|--------|----|

| intern | A  |

| extern | В  |

| SIO-Takt:<br>CTC-Betr.Art:                  | x16<br>Zähler                 | x32<br>Zähler                  | x64<br>Zähler         | x16<br>Zeit-<br>geber |

|---------------------------------------------|-------------------------------|--------------------------------|-----------------------|-----------------------|

| BAUDRATE                                    | C                             | C-Teilerfak                    | tor                   |                       |

| 9600<br>4800<br>2 400<br>1200<br>600<br>300 | 13<br>26<br>52<br>10 4<br>208 | 13<br>26<br>52<br>10 4<br>20 8 | 13<br>26<br>52<br>104 |                       |

| 150                                         |                               |                                | 208                   |                       |

| 110                                         |                               |                                |                       | 142                   |

| 75                                          |                               |                                | ·                     | 208                   |

Programmiertabelle zur Einstellung verschiedener Baudraten über einen CTC-Kanal.

# 3.2.5 Parallelschnittstelle

Die Baugruppe stellt über einen Baustein Z&A-PIO 16 fest verdrahtete Ein-/Ausgänge, sowie 4 Handshake Leitungen zur Verfügung (nur PSI&O(D)/M-Reihe).

Die Adressen des PIOs sind:

PORT A - OCH PORT B - ODH

Alle 16 Datenleitungen sind mit nicht invertierenden Schmitt-Trigger Bausteinen gepuffert. Sie sind so angeordnet, daß damit Drucker mit Parallelschnittstelle (Centronic-Schnittstelle), sowie Winchester Laufwerke PSI/WINS angeschlossen werden können. Der Abgriff der Signale erfolgt über den 26-poligen Stecker ST-C. Dieser ist 1:1 auf dem vierten (von unten) 25-poligen Stecker der Rückwand verdrahtet.

| PIO-Anschluß                                         | Richtung                                            | Signalname                                                    | Steckerbel egung                                             |

|------------------------------------------------------|-----------------------------------------------------|---------------------------------------------------------------|--------------------------------------------------------------|

| PAO PA1 PA2 PA3 PA4 PA5 PA6 PA7                      | Output Output Input Input Input Input Output Output | STROBE I PRIME FAULT EMPTY BUSY SELECT SPARE direction Port B | C-12<br>C-11<br>C-23<br>C-22<br>C-21<br>C-20<br>C-25<br>C-10 |

| ARDY<br>ASTR                                         | Output<br>Input                                     |                                                               | C-7<br>C-8                                                   |

| BSTR<br>BRDY                                         | Input<br>Output                                     |                                                               | C-2 4<br>C-5                                                 |

| PB0<br>PB1<br>PB2<br>PB3<br>PB4<br>PB5<br>PB6<br>PB7 | bidirectional  n  n  n  n  n                        | DATA O DATA 1 DATA 2 DATA 3 DATA 4 DATA 5 DATA 6 DATA 7       | C-19<br>C-17<br>C-18<br>C-16<br>C-4<br>C-3<br>C-2<br>C-15    |

| -                                                    | -                                                   | Vec (5Volt)<br>GND (0Volt)                                    | C-13/26<br>C-1/14                                            |

Die Signalbezeichnung entspricht der weitverbreiteten Centronics-Schnittstelle. Port A und Port B können durch Ersetzen der Treiberbausteine Anwenderseitig umdefiniert werden.

Port B ist mit bidirektionalen Puffern (IC1: 74LS245) versehen. Ihre Richtung wird durch Bit 7 von Port A festgelegt.

| Port A - Bit 7 | Richtung IC1    |

|----------------|-----------------|

| 0              | Input<br>Output |

Alle unidirektionalen Eingänge sind mit 1 kOhm Pull Up-Widerständen versehen.

Die Treiberkapazität aller Ausgänge beträgt ca. 24 mA bei log. Null Pegel.

Die Strobe-Leitung für PORT B ist auch an den CPU/DMA-Sockel (Pin 41) der Baugruppe geführt. Sie dient dort als Ready-Signal für DMA-gesteuerte Datenübertragungen über die Parallelschnittstelle.

# 32.6 Zähler-/Zeitgeber-Kanäle

Die Zentralbaugruppe KDT5 enthält zwei Z80 A-CTC Bausteine

CTC-1 - Basisadresse: 08H CTC-2 - Basisadresse: 10H

# Verwendung der Kanäle:

CTC-1 Kanal 0 - Interrupt FD-Controller uP 765 Kanal 1 - Baudrate SIO-Port B

Kanal 2 - Baudrate SIO-Port A

Kanal 3 - frei für Anwender-Verwendung

CTC-2 Kanal 0 - Tongenerator

Kanal 1 - Tastatur Interrupt

Kanal 2 - Vsync Interrupt (Systemtakt für Multitasking)

Kanal 3 - frei für Anwender-Verwendung

# 32.7 Floppy Disk Controller und Floppy Disk Laufwerke

Die Floppy Disk Controller Schaltung der Baugruppe ermöglicht den Betrieb von Mini- und/oder Standardlaufwerken mit einfacher und/oder doppelter Schreibdichte (single/double density). Die entsprechende hard- und softwaremäßige Festlegung erfolgt fabrikseitig entsprechend der bestellten PSI80(D)-Version.

Das Herz des Controllers ist der Baustein NEC uP 765, der als intelligenter Peripherieprozessor alle wesentlichen Aufgaben der FD-Ansteuerung übernimmt. Vier Laufwerke mit 'single' und/oder 'double head Ausrüstung können angeschlossen werden.

Dem Bau: tein uP 765 sind vier E/A-Adressen zugeordnet:

14H - Main Status Register

15H - Data Register

Data Acknowledge (für DMA basierende Datentransfers)

1FH - Terminal Count

Über Kanal O. von CTC-1 ist der uP 765 im Z80A-System interruptfähig. Die Leitung DRQ (Data Request) ist zur Steuerung von DMA-gesteuerten Datenübertragungen zwischen uP 765 und Speicher an den CPU/DMA-Sockel der Baugruppe geführt (Pin 43).

Zur Steuerung der Disk Controller Hardware dienen folgende Bits des Statusports:

```

Laufwerkstyp (Umschaltung der Controller Hardware):

ST-6

0 ---> 8"-Laufwerke

1 ---> 5 1/4"-Laufwerk

Motor On (für 5 1/4"-Laufwerke):

ST-7

0 ---> Motor ausgeschaltet

1 ---> Motor eingeschaltet

```

# Anschluß von Laufwerken

Der Anschluß erfolgt am 34-poligen Stecker ST-D über eine 1:1 Verbindung.

| Anschl                                                             | uß ST-E                                               | Signalbezeichnu                                                                                 | ng     | Bemerkung                                  |

|--------------------------------------------------------------------|-------------------------------------------------------|-------------------------------------------------------------------------------------------------|--------|--------------------------------------------|

| D-4 i                                                              | output<br>input<br>input                              |                                                                                                 |        | ufwerke)<br>nicht vorhanden: J11<br>ossen) |

| D-10 c<br>D-12 c<br>D-14 c                                         | output<br>output                                      | Index Drive Select 1 Drive Select 2 Drive Select 3 Motor On                                     |        | "-Laufwerke)                               |

| D-20 o<br>D-22 o<br>D-24 o<br>D-26 i<br>D-28 i<br>D-30 i<br>D-32 o | output<br>output<br>input<br>input<br>input<br>output | Direction Step Write data Write gate Track 0 Write protect Read Data Head Select Drive Select 4 | (für d | ouble sided drives)                        |

Alle Ausgänge zum Laufwerk werden von Open Collector Puffern getrieben. Alle Eingänge vom Laufwerk sind mit 150 Ohm Pull Up-Widerständen versehen. Die ungeraden Anschlüsse von ST-D liegen auf Masse.

In Kontron PSI80/82-Systeme sind folgende Floppy Disk Laufwerke eingesetzt:

```

MPI B102

PSI80Q/xx

MPI B101

PSI82D/xx

Micropolis 1015/II PSI80D/xx

```

Kontron behält sich den Einsatz äquivalenter Laufwerke vor. Diese Laufwerke arbeiten mit 100 tpi. Die hardwaremäßige Adressierung ist:

ungerade Adressen: linkes Laufwerk gerade Adressen: rechtes Laufwerk

# 3.2.8 Video Controller

Der Videocontroller der Baugruppe ist um den Controller CRTC-6845 aufgebaut. Diesem Baustein sind zwei I/O-Adressen zugeordnet.

18H - Adrebregister 19H - Registerfile

Folgende Bits des Statusports dienen zur Steuerung der Video Controller Hardware:

ST4 - Umschaltung zwischen alphanumerischer und graphischer Betriebsart

ST4=0 --> Graphische Betriebart ST4=1 --> Alphanumerische Detriebsart

ST3 - Invertierung des gesamten Bildes

ST3=0 --> Hintergrund dunkel ST4=1 --> Hintergrund hell

Die Invertierung einzelner Zeichen erfolgt im alchanumerischen Modus bei gesetztem achten Bit im ASCII-Code des abzubildenden Zeichens.

Die Taktfrequenz für die Steuerung de Videocontrollers wird von einem eigenen Oszillator mit 12.36 MHz (Kontron PSI80) bzw. 13.5 MHz (Kontron PSI82) erzeugt.

Dies entspricht Bildfrequenzen von 50 bzw. 60 Hz.

# Bildwiederholspeicher

Der Bildwiederholspeicher liegt im Adreßbercich von 8000H - BFFFH und kann von der CPU aus durch Memory mapping erreicht werden (siehe Kapitel Speicher).

Der Bildwiederholspeicher ist für CPU-7 griffe transparent. Dies ermöglicht virtuell einen gleichzeitigen Zugriff von CPU und CRTC. Die Synchronisation von CPU-Zugriffen erfolgt über die WAIT-Leitung der CPU.

# Zeichensatz im Alpha-Modus

Der Zeichensatz ist durch PROM8 festgelegt. Einem Zeichen sind 16 Bytes zugeordnet, von denen die ersten 10 jeweils das Bitmuster einer Bildschirmzeile (Matrix 8x10) beschreiben. Der ASCII-Code (OOh...FFh) \*16 des darzustellenden Zeichens aus dem Bildwiederholspeicher adressiert das erste Byte (= die oberste Zeile der Matrix), die folgenden \*9 Zeichen werden vom Videocontroller nacheinander adressiert. ASCII-Zeichen unter 20H werden vom Bildschirmtreiber \$MON ausgewertet. Im zugehörigen PROM-Bereich sind Sonder- und Semigraphik-Zeichen enthalten, die über Codes > 80H angesprochen werden können.

# Cursorsteuerung

Die Programmierung des Videocontrollers erfolgt unter KOS in den Modulen \$MON, \$GRAP und XMON.

Die direkte Programmierung über die E/A-Adressen 18H (Registeradreßport) und 19H (Steuerregister) ist möglich unter Interruptsperre.

Es wird zuerst in 18H die Adresse des zu ändernden Steuerregisters geschrieben, anschließend wird das Steuerregister gelesen oder beschrieben.

### a) Cursor-Format

Steuerregister 10 beeinflußt die Cursordarstellung:

ZZ

ZZZZ = Endzeile (für Cursorgröße)

# b) Cursor-Positionierung

Die Cursor-Positionierung erfolgt stets relativ zur Scroll-Adresse (= 1. Zeichen am Bildschirm) durch KOS-Aufrufe.

1

# Monitoranschluß

Alle benötigten Signale sind an dem 26-poligen Stecker ST-K herausgeführt.

# Anschluß ST-K Signalbezeichnung

K-2 cutput Video

K-3 output VSTPA (\*)

K-4 input Light Pen Strobe

K-5 output Composite Video

K-6 input VSTOP (\*)

K-7 output Horizontal Sync (HSYNC)

K-8 output Vertical Sync (VSYNC)

K-9 input ext. Clock in (\*)

Alle anderen Anschlüsse liegen auf Masse.

Alle Ein-/Ausgänge mit Ausnahme des Composite Video Signals sind TTL-kompatibel.

Das Signal LIGHT PEN STROBE kann über Kanal 3 von CTC-1 einen Interrupt generieren.

Das composite Video-Signal ist auf eine 75 Chm BNC-Buchse geführt.

Für Kontron PSI80-Systeme werden Bildschirme vom Typ QDM-SN, Phosphor P39, Hersteller 3Q, verwendet, der Einsatz äquivalenter Typen bleibt vorbehalten.

Für Kontron PSI82-Systeme kommen Monitore Grundig BG33 oder ein äquivalenter Typ zum Einsatz zum Anschluß von externen Bildschirmen.

(\*) nicht verwendet.

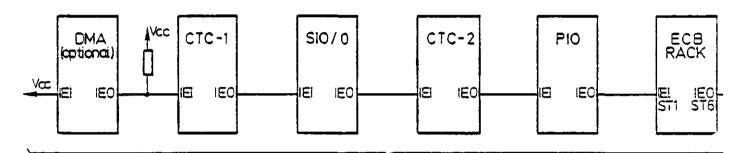

# 3.2.9 Interruptpriorität

Auf der Baugruppe ist folgende Interruptpriorität festgelegt:

- 1. DMA (falls bestückt)

- 2. CTC-1

- 3. SIO

- 4. CTC-2

- 5. PIO

- 6. Einschubrahmen

In der Standardversion ist Kanal O von CTC-1 (Disk Interrupt) die höchste Priorität zugeordnet.

Die Z80 A-CPU ermöglicht vektorisierte Interrupts. Dazu stellt die CPU selbst im I-Register die frei in Schritten von 256 Byte wählbare Basisadresse xx00H der aktuellen Interrupttabelle zur Verfügung. Von den Peripheriebausteinen wird in 8 Bits (Format: yyyyyy0B) einer aus den 128 möglichen Einsprüngen in die Interrupttabelle definiert.

Dazu ist das Vektorregister der Z&A-Peripheriebausteine über Steuerbefehle entsprechend zu setzen. Die Einträge in der Interrupttabelle werden als Anfangsadressen der zu jedem Interrupt zugehörigen Beantwortungsroutinen (ISR = Interrupt Service Routine) aufgefaßt. Vom Betriebssystem KOS ist der Speicherbereich von

# xx00H bis xxFFH

für die Interrupttabelle reserviert. Der Wert xx kann aus dem I-Register der CPU abgelesen werden (KDM-Kommando). Innerhalb der Interrupttabelle sind die Einträge von xxEDH bis xxFFH für das Betriebssystem reserviert.

# Bild 2: Interrupt priorität im PSI80/D-System

PSI 80/D-Zentralboard

# 3.2.10 Lautsprecher- und Resetanschluß

Stecker ST-J dient zum Anschluß des Lautsprechers und des Resetschalters.

| J-1              | GND            | J <b>–</b> 6     | GND                          |

|------------------|----------------|------------------|------------------------------|

| J <b>–</b> 2     | GND            | J <del>-</del> 7 | LAUTSTÄRKE POTI (Empfohlener |

| J <b>-</b> 3     | RESET-SCHALTER |                  | Wert: 220-470 Ohm)           |

| J-4              | GND            | J <b>-</b> 8     | GND                          |

| J <del>-</del> 5 | LAUTSPRECHER   | J-9              | GND                          |

|                  |                | J <b>-</b> 10    | GND                          |

# 4. Zusatzbaugruppen

# 4.1 CPU/DMA-Adapter

Die CPU/DMA-Adapterplatine (Option PSI/DMA) dient zur Erweiterung der PSI80(D)-Zentralplatine um einen Z80A-DMA Baustein.

Die Platine wird als Piggy Back Baugruppe anstelle der CPU in den 48poligen CPU/DMA-Sockel der Baugruppe eingesetzt. Hierbei ist bei nachträglicher Montage darauf zu achten, daß der überstehende Teil der Adapterplatine in Richtung Z&DA-PIO der zentralen Rechnerplatine zeigt.

Die Baugruppe enthält neben CPU und DMA (I/O-Adresse: 0) einen Miltiplexer (74LS153), mit dem 4 verschiedene Eingangssignale auf den Ready Eingang des DMA-Bausteins geschaltet werden können. Der Multiplexer ist softwaremäßig über ein Register (AM 2918) einstellbar. Dieses Register kann als I/O-Port beschrieben und gelesen werden (E/A-Adresse: 01: x = beliebiger Wert):

| D7D0       | DMA-Ready    | von                        |

|------------|--------------|----------------------------|

| xxxx xx 00 | FDC-DRQ      | Floppy Disk Controller 765 |

| xxxx xx 01 | DMA-Ready    | von ECB-Bus Pin 22a        |

| xxxx xx 10 | STR-B        | von PIO Port B-Strobe      |

| xxxx xx 11 | Wait/Ready A | von SIO Wait/Ready Port A  |

# Achtung:

Die Verwendung des DMA-Bausteins wird vom Standardbetriebssystem KOS 5.x nicht unterstützt. Es ist also Sache eines Anwenderprogramms, welche Funktion der DMA-Baustein im System erfüllt.

# 42 RS 422/423-Option

Liese Option für die Serienschnittstellen ist Teil der Option 'LS', die den Anschluß als Slavestation oder Software-Master (Option MS-SOFT) an Kontron KOBUS-Systeme ermöglicht.

Die SIO-Adapterplatine (Platinen Nummer: 384) realisiert für den Serienkanal A der PSI80/82-Rechnerplatine (KDT Rev. 5.x) eine zu den elektrischen Spezifikationen der RS422-Norm kompatible serielle Schnittstelle. Eine derartige Schnittstelle wird für den Anschluß der KIA-Einheit (KOBUS Interface Adapter) benötigt. Die RS422-Schnittstelle ermöglicht hohe Übertrgungsraten (Megahertz-Bereich) bei vergleichsweise langen Leitungen (bis 20 Meter).

# Einbauhinweise:

Der SIO-Adapter ist als 'Piggy Back Board' für die KDT-Platine ausgeführt und wird anstelle des SIO-Bausteins (IC 18) in dessen Fassung eingesetzt. Es ist unbedingt sicherzustellen, daß folgende Bauteile der KDT-Platine zuvor entfernt werden:

- IC 17 75189 a) b) IC 19 -75188

- c) IC 20 -75189

- d) Jumper J2, J3, J4

Durch die Entfernung von IC17 entfällt auch die Möglichkeit, den Sender-/Empfängertakt für Kanal B des Z&A-SIO von außen über die RS232C-Schnittstelle einzuspeisen.

Die Verbindung vor SIO-Adapter zur Rückseite des PSI80-Systems erfolgt über den Anschluß ST-F der Adapterplatine. Es wird das für Kanal A (KDT Stecker ST-F) vorhandene 26-polige Flachbandkabel verwendet. Dieses Kabel stellt eine 1:1 Verbindung mit dem zweiten Stecker von unten an der Rückseite des PSI80-Systems her.

# Steckcrbelegung:

| Anschlußpin                   |                                      | Signal                                                                                                  |                                                           |

|-------------------------------|--------------------------------------|---------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|

| 2,14 3,15 4,16 5,17 6,18 7,19 | DTRA -<br>RxDA -<br>DCDA -<br>TxCA - | Transmitter Data Data Terminal Ready Receiver Data Data Carrier Detect Transmitter Clock Receiver Clock | (Output) (Output) (Input) (Input) (Input) (Input) (Input) |

<sup>1, 8, 11-13, 24-26</sup> GND 9, 10, 21-23

Diese Steckerbelegung ermöglicht wiederum eine 1:1 Verbindung mit der in Kontron KOBUS-Systemen notwendige KIA-Einheit (Flachband- oder Rundkapel).

# 4.3 Modem-Option

Diese Option zur PSI80(D)-Serienschnittstelle B setzt die SIO-Schnittstelle auf die Datenendeinrichtungs-Schnittstelle um. Betriebsart: manuell, Betriebsweise duplex, Gleichlaufverfahren asynchron, Übertragungsgeschwindigkeit 1200 bit/s Zulassungsnummer FTZ 02013D PSI80.

# 4.4 Softwareschutz-PROM

Auf KDT5-Platinen ist der Steckplatz PROM5 vorgesenen zur Aufnahme eines anwenderseitig erzeugten Softwareschutz-PROMs vom Typ nm 7603.

Der Strobe von PROM5 wird unter der I/O-Adresse 1BH angesprochen. Durch die Befehlssequenz

LD C, 1BH

LD B, PROMADDR

IN A, (C)

wird das Byte in PROMADDR ausgelesen. Dieser Wert kann mit Kennziffern verglichen werden. PROM5 enthält 32 Bytes. Der Anfangswert von PROMADDR ist 0, der größte Wert ist 31 x 8, da PROMADDR in Schritten von 8 inkrementiert wird. Die Adreßeingänge von PROM5 sind IA11...IA15.

1 1 1 1

# 5. Beschreibung des Einschubrahmens

In den Versionen der PSI80x/Mx ist ein zusätzlicher Einschubrahmen im Inneren des Gehäuses hinter dem Sichtschirm vorhanden.

Er ermöglicht den Einsatz von ECB-Karten im Europaformat (160x100 mm). Jeweils 2 nebeneinanderliegende Steckplätze können stattdessen auch eine Karte im Doppel-Europa-Format (230x160 mm) enthalten.

Träger dieser Karte ist eine gedruckte Schaltung, die den Kontron ECB-Bus realisiert. Über ein 64-poliges Kabel ist diese Platine mit der zentralen Computerbaugruppe verbunden.

# 5.1 Kontron's ECB-Bus Standard

Zu diesem Bus sind Karten für die Realisierung der vielfältigsten Aufgaben von vielen Herstellern aus Westdeutschland, Österreich, Schweiz. Schweden, Niederlande und Frankreich verfügbar.

Wir weisen darauf hin, daß im PSI80 auch dieser Bus mit 4 MHz Taktfrequenz betrieben wird: Es sind somit Karten der Z80A-ECB-Reihe zu verwenden.

Bei externer Speichererweiterung genügt die Klasse -3 (Zugriffszeit 250 ns) für RAM's. Bei PROM's sind im allgemeinen Typen mit einer garantierten Zugriffszeit von 350 ns ausreichend. wenn sichergestellt ist, daß die Umgebungstemperatur außerhalb des Gehäuses 35 Grad C nicht übersteigt.

Über Einzelheiten der ECB-Reihe informieren Kontron's ECB-Handbücher.

# ECB-Bus Pin-Belegung:

|              | Benennung | Stecker Pi                                                                                                         | n Bezeichnung        |

|--------------|-----------|--------------------------------------------------------------------------------------------------------------------|----------------------|

|              |           |                                                                                                                    |                      |

| Adreabus:    | AO        | 5c                                                                                                                 | Adresse O            |

|              | A1        | 7c                                                                                                                 | Adresse 1            |

|              | A2        | 6а                                                                                                                 | Adresse 2            |

|              | · A3      | 6e                                                                                                                 | Adresse 3            |

|              | A4        | 7a                                                                                                                 | Adresse 4            |

|              | A5        | ða                                                                                                                 | Adresse 5            |

|              | A6        | 9a                                                                                                                 | Adresse 6            |

|              | A7        | 9c                                                                                                                 | Adresse 7            |

|              | A8        | 8c                                                                                                                 | Adresse 8            |

|              | A9        | 30a                                                                                                                | Adresse 9            |

|              | A10       | 18c                                                                                                                | Adresse 10           |

|              | A11       | 17c                                                                                                                | Adresse 11           |

|              | A12       | 27c                                                                                                                | Adresse 12           |

|              | A13       | 29a                                                                                                                | Adresse 13           |

|              | A14       | 18a                                                                                                                | Adresse 14           |

|              | A15       | 28c                                                                                                                | Adresse 15           |

|              |           | الشيوة في ها جو الحال المساولة عن المساولة المساولة المساولة المساولة المساولة المساولة المساولة المساولة المساولة |                      |

| Datenbus:    | $\infty$  | 2c                                                                                                                 | Data O               |

|              | D1        | 14c                                                                                                                | Data 1               |

|              | D2        | 40                                                                                                                 | Data 2               |

|              | D3        | 4a                                                                                                                 | Data 3               |

|              | D4        | 5a                                                                                                                 | Data 4               |

|              | D5        | 2a                                                                                                                 | Data 5               |

|              | D6        | 3a                                                                                                                 | Data 6               |

|              | D7        | 3c                                                                                                                 | Nata 7               |

| Bank Select: | _MR 90    | 10 c                                                                                                               | Memory Bank Select 0 |

|              | -MBS1     | 12c                                                                                                                | Memory Bank Select 1 |

|              | -MBS2     | 13c                                                                                                                | Memory Bank Select 2 |

|              | -MBS3     | 14a                                                                                                                | Memory Bank Select 3 |

|              | -MBS4     | 23c                                                                                                                | Memory Bank Select 4 |

|              | -MBS5     | 19c                                                                                                                | Memory Bank Select 5 |

|              |           | 1 JC                                                                                                               |                      |

# Hinweis:

Aktiv-Low-Signale sind mit einem Minuszeichen ge-

kennzeichnet.

Alle Bussignale dürfen mit ca. 7 TTL-Eingängen belästet

werden (ca. 30 LS TTL-Lasten).

|                | Benennung                                            | Stecker Pin                                          | Bezeichnung                                                                                 |     |                          |

|----------------|------------------------------------------------------|------------------------------------------------------|---------------------------------------------------------------------------------------------|-----|--------------------------|

| Steuerbus:     | -M1<br>-MRQ<br>-IORQ<br>-RD<br>-WR<br>-RFRSH<br>-HLT | 20 a<br>30 c<br>27 a<br>24 c<br>22 c<br>28 a<br>25 c | Maschinenzyklus 1<br>Memory Request<br>IN/OUT Request<br>Read<br>Write<br>Refresh<br>Halt   |     |                          |

| Verschiedenes: | -WAIT<br>-INT<br>-NMI<br>-RESET                      | 10c<br>21c<br>20c<br>31c                             | Wait<br>Interrupt<br>non maskable Int.<br>Reset (Ausgang)                                   |     |                          |

|                | IEI<br>IEO                                           | 11c<br>16c                                           | Int. enable in Int. enable out                                                              |     |                          |

|                | -PWRCL<br>CLK<br>2 x CLK<br>n x CLK                  | 26c<br>29c<br>16a<br>25a                             | Power on clear<br>Clock 4.0 MHz<br>(MOS-Pegel)<br>2 x Clock<br>n x CLOCK                    | (1) | (1)<br>(3)               |

|                | -BUSRQ<br>-BUSAK<br>-BAI<br>-BAO                     | 11a<br>31a<br>12a<br>17a                             | Busrequest Busacknowledge Busprioritäts- steuerung Ein Busprioritäts- steuerung Aus         |     |                          |

|                | WRITE EN<br>DPR                                      | 26a<br>23a                                           | Write Enable                                                                                |     |                          |

|                | +5<br>GND<br>+12<br>- 5<br>+15<br>-15<br>VCMOS       | 1a,c<br>32a,c<br>13a<br>15a<br>19a<br>15c<br>24a     | + 5V Ground + 12V für EPROMs - 5V für EPROMs + 15V für V24 und - 15V für AD-Wand (Notstrom) |     | (2)<br>(2)<br>(2)<br>(2) |

+

<sup>(1)</sup> wird von der Kontron PSI-Zentralplatine nicht bereitgestel\_t.

<sup>(2)</sup> Nicht mit Kontron PSI-Zentralplatine verbunden, Versorgung vom Netzteil direkt über Lötbrücken auf der Einschubplatine

<sup>(3)</sup> nicht durchverbunden

# 5.2 Adressierung im ECB-Bus

Der 'Externe Erweiterungsbus' des Einschubrahmens ist elektrisch ständig an die Busse der Zentralplatine angekoppelt. Baugruppen des Einschubrahmens dürfen bei folgenden Gelegenheiten Daten auf den Bus schalten:

- a) Die CPU liest von Ein-/Ausgabeadressen größer oder gleich 20H. Dementsprechend sind auf den Erweiterungskarten Bausteine nur mit Adressen größer/gleich 20H adressierbar.

- b) Die CPU liest den Interruptvektor eines externen Peripheriebausteins (siehe Interruptpriorität).

- c) Die CPU liest von einem externen Speicher (siehe hierzu Abschnitt: Speicher)

Dies gilt nicht für den Betrieb eines autonomen Subsystems (z.B. Z&DA-ECB/C8). Bei diesem Aufbau entfällt das 64-polige Verbindungskabel zur Zentralplatine und das Subsystem wird z.B. über eine Serienschnittstelle angekoppelt.

Beim Einsatz von ECB-Karten im PSI80 sind folgende Port-Adressen standardmäßig verwendet:

| Platine                                                                                  | E/A-Adresse                                                 | fest/variabel                                                          |

|------------------------------------------------------------------------------------------|-------------------------------------------------------------|------------------------------------------------------------------------|

| Z80 A-ECB/A Z80 A-ECB/B Z80 A-ECB/I Z80 A-ECB/X Z80 A-ECB/O Z80 A-ECB/AE16 Z80 A-ECB/AA4 | COHC3H, 3OH4FH<br>2OH2FH<br>AOH<br>DOH<br>EOH<br>8CH<br>4OH | fest fest (für PSI/BASIC) variabel variabel variabel variabel variabel |

Die E/A-Adressen der ECB/A und ECB/B sind fest eingestellt. Die Baugruppen-Adressen der restlichen Karten wird bei Konfiguration im Werk auf obigen Wert eingestellt.

Bei mehr als 2 Karten gleichen Typs werden die darauf folgenden Adressen eingestellt, sofern dies mit anderen eingebauten Karten vereinbar ist (z.B. 4xZ80A-ECB/I: AOH, BOH, COH, DOH, falls keine ECB/A zusätzlich eingebaut ist).

# 5.3 Interruptsteuerung im Einschubrahmen

In Z80A-Systemen sind Interrupts hardwaremäßig durch die fest verdrahtete Daisy chain Kette in ihrer Priorität festgelegt.

Die Priorität im Einschubrahmen ist wie folgt:

| - | <ul> <li>Steckplatz</li> </ul> | 1 | im | Einschubrahmen | höchste Pr | iorität   |

|---|--------------------------------|---|----|----------------|------------|-----------|

| - | - Steckplatz                   | 2 |    | tt .           |            |           |

| - | - Steckplatz                   | 3 |    | 11             |            |           |

| - | - Steckplatz                   | 4 |    | n              |            |           |

|   | <ul> <li>Steckplatz</li> </ul> | 5 |    | 11             |            |           |

| _ | - Steckplatz                   | 6 |    | 1f             | niedrigste | Priorität |

Bein Anordnen von interruptfähigen Karten im Einschubrahmen ist darauf zu achten, daß die Durchschleifung von der in der Priorität niedrigsten Platine bis zum Anschlußkabel ununterbrochen ist. Die Durchschleifung auf der Platine des Einschubrahmens ist also auf den eingesteckten Platinen so fortzusetzen, daß alle interruptfähigen Bausteine einbezogen sind.

Die Durchschleifung der Signale IEI/IEO ist zeitkritisch: wie auf der Zentralplatine (siehe Schaltplan) ist bei längeren Ketten eine Look-ahead Logik vorzusehen.

Weitere Informationen sind in Applikationsschriften zur Interruptbehandlung von Kontron enthalten.

# 5.4 Stromversorgung des Einschubrahmens

Über einen 7-poligen Stecker werden dem Einschubrahmen alle Spannungen des PSI80-Netzteils zugeführt.

Die Spannungen sind wie folgt belastbar:

|       | PSI80/M2 | PSI80/M1 | PSI80/MD |  |  |

|-------|----------|----------|----------|--|--|

| + 5V  | 3.0 A    | 3.3 A    | 3.6 A    |  |  |

| + 127 | 0.2 A    | 0.7 A    | 1.2 A    |  |  |

| + 15V | 0.2 A    | 0.2 A    | 0.2 A    |  |  |

| - 15V | 0.2 A    | 0.2 A    | 0.2 A    |  |  |

Die 5V-Versorgung erfolgt direkt. Die anderen Spannungen sind mit auf der Platine des Einschubrahmens zu schließenden Lötbrücken geführt. Durch Einsetzen eines Festspannungsreglers des Typs 7905 kann aus -15V die für manche Speicherplatinen notwendige -5V-Versorgung realisiert werden. Der Alatz dafür ist vorgesehen.

# 6. Nets.teil

Das Netzteil der Kontron PSI80/82-Systeme ist sekundär getaktet (+5V, +12V). Die Nebenspannungen (+15V, -15V, -12V) werden durch Festspannungsregler erzeugt.

Jede Baugruppe im System ist über ein eigenes Kabel versorgt.

Die zusätzliche Belastbarkeit ist gemäß den Spezifikationen in den Systemen mit Einschubrahmen vorgesehen. In den anderen Ausführungen der Kontron PSI®-Serie sind nur die Spannungen +5V, +12V und -12V garantiert.

Alle Spannungen sind kurzschlußfest und gegen Überstrom und Überspannung geschützt.

# 7. Festplattenanschluß

Im Kontron PSI80x/W5- und PSI82D/W5-System erfolgt der Anschluß der 5Mio-Byte Festplatte (Typ Seagate ST506 oder Äquivalent) über die Controllerbaugruppe ECB/HC mit Datenseparator ECB/DS, die in den Einschubrahmen eingesteckt werden.

# 7.1 Funktionseinheiten

Die Baugruppe ECB/HC enthält folgende Funktionseinheiten:

- ECB-Bus Interface mit I/O-Adresdekoder

- Disk I/O-Prozessor 9056 der Firma MSC

- Laufwerk Interface zum ST506 der Firma Seagate

- Datenseparator Interface our ECB/DS

# 7.2 Schaltungsbeschreibung

### ECB-Interface

Die ECB/HC ist vom Bus betrachtet eine Ein-/Ausgabebaugruppe. Das ECB-Interface besteht deshalb aus einem E/A-Adreßdekoder, sowie einigen Buspuffern bzw. Datenein-/ausgaberegistern.

# a) E/A-Adreßdekoder

Die Baugruppe beansprucht den Adreßraum für 4 E/A-Adressen, wovon allerdings nur 2 Verwendung finder. Über einen 6-fach Schalter wird die Baugruppenadresse festgelogt. Ein 6 Bit-Vergleicher vergleicht die Stellung des Schalters F2 mit den Adreßbits A2...A7.

# Beispiel:

| Adresse(hex) | -WR=Low           | -WR=High           |

|--------------|-------------------|--------------------|

| 80           | Data Write Reg.   | Data Read Reg.     |

| 81           | nicht ver         | wendet             |

| 82           | Status Write Reg. | Status Read Buffer |

| 83           | nicht ver         | wendet             |

# b) Data Write Register (DWR)

Über dieses Register erfolgt der Datentransfer vom ECB-Bus zum Disk I/O-Prozessor 9056 der ECB/HC. Es werden entweder Kommandos oder Daten im eigentliche Sinne übertragen, Bei Datenübertragungen zum oder vom Disk I/O-Prozessor sind dessen Statussignale zu beachten.

c) Data Read Register (DRR)

Über dieses Register erfolgt der Datentransfer vom Disk I/O-Prozessor 9056 über den ECB-Bus zum Rechner. Es werden entweder Statusrückmeldungen oder Daten im eigentlichen Sinne übertragen.

d) Status Write Register (SWR)

Das SWR ist ein 4 Bit Register, über das Steuereingänge des 9056 Moduls programmierbar sind.

e) Status Read Buffer (SRB)

Über den SRB können vier Statussignale des 9056 Moduls in den Rechner eingelesen werden. Dies sind:

DO - 9056 Anschluß 16: -RDY

D1 - 9056 Anschluß 1: -LDI

D6 - 9056 Anschluß 17: BUSY

D7 - 9056 Anschluß 2: -DOUT

# 7.3 Disk I/O-Prozessor MSC 9056

Der Disk I/O-Prozessor MSC 9056 ist auf der Lötseite der ECB/HC bestückt. Dieses Modul empfängt Kommandos über den ECB-Bus und führt diese selbständig aus. Ein Modul-interner Sektorpuffer ermöglicht zusammen mit den Handshake Mechanismen des Moduls Transfergeschwindigkeiten, die unabhängig von der Übertragungsrate des angeschlossenen Winchesterlaufwerks sind. Der Datentransfer über den ECB-Bus erfolgt programmgesteuert (programmed I/O über normale IN/OUT-Befehle).

# 7.4 ST506-Laufwerk Interface

Der Anschluß eines 5 1/4 Zoll Winchesterlaufwerks erfolgt über den 34poligen Stecker ST-B der ECB/HC. Die Steckerbelegung ermöglicht eine

1:1 Verdrahtung zwischen ECB/HC und ST506. Dort ist der Anschluß J1 zu

verwenden. Der Datenanschluß über differentielle Leitungen befindet

sich auf der Aufsteckplatine ECB/DS, Stecker ST-B (A = Ausgang, E =

Eingang):

```

A-RED. CURRENT

4

A-HEAD2

(nicht angeschlossen auf ST506)

6

A-WR.GATE

8

E-SEEK COMPLETE

10

E-TRACK O

E-WRITE FAULT

12

14

A-HEAD O

16

(nicht angeschlossen auf ST506)

18

A-HEAD 1

20

E-INDEX

E-READY

22

24

A-STEP

26

A-DRS O

(Drive Select)

28

A-DRS 1

(Drive Select)

30

A-DRS 2

(nicht angeschlossen auf ECB/HC)

<u>3</u>2

A-DRS 3

(nicht angeschlossen auf ECB/HC)

34

A-DIRECTION

```

# 7.5 ECB/DS - Anschluß

Der Anschluß der ECB/DS (Datenseparator) erfolgt unmittelbar durch Aufstecken der ECB/DS auf Stecker ST-C (20-polig) der ECB/HC. Die entstehende Baugruppenkombination beansprucht etwa 3 Steckplätze eines ECB-Einschubrahmens. ST-C ist folgendermaßen belegt:

```

RDGATE

(Read Gate)

PLO-CLOCK

3

CLEAR

4

SELO

5 6

7

8

RDDATA

(Read Data)

SEL1

WR.GATE

(Write Gate)

(Write Address Mark)

-WAM

9

10

(Reset Precompensation)

-KILL. PREC

WR. DATA

(Write Data)

11

-15 Volt

12

AMD

(Address Mark detect)

13

-13 Volt

DR.SELO

14

(Drive Select 0)

15

GND

16

DR.SEL1

(Drive Select 1)

17

GND

18

-RESET

(Reset Read Logic)

19

Vcc

(+5 Volt Versorgung)

20

Vcc

```

1 111 1

# **KONTRON DEUTSCHLAND**

8057 Eching b Munchen

Breslauer Straße 2

Tel (089) 319 01 313

Telex 522122

Telefax (089) 319 01 311

Telex 5213671

Telex 5213671

8057 Eching Obere Hauptstraße 5 Tel. (0.89) 3.19.01.318 Telex 5.213.671

8500 Nurnberg 20 Rennweg 60/62 Tel (09 11) 53 33 06 Telex 6 26 391

7000 Stuttgart 30 6000 Frenkfurt 70 Maybachstraße 39 Kennedy Allee 34 Tel (061) 63 60 61 Telex 723 061 Telex 414 881

4000 Dusseldorf 1 Ronsdorfer Str 145 Tel (0211) 7331453 Telex 8582675 Telex 8582675

2000 Hamburg 70 Konigsreihe 2 Tel (040) 6825 0 Telex 211998

1000 Berlin 41 Albrechtstraße 34 Tei (030) 7923031 3 Telex 185484

# **KONTRON INTERNATIONAL**

AUSTRALIA KONTRON (Pty ) Ltd Warringah Mail Brookvale NSW 2100 Phone 00 61 2 938 3433 Telex 0071 27012

AUSTRIA

KONTRON Gmbh&Co KG

Esgrubengasse

A 2334 Vosendor/tb Wien

Phone 0043 222670 631

Tetex 0047 131699

BELGIUM

Gulden p v b a

Gulden Sporeniaan 19

8 9220 Merelbeke

Phone 0032 91 301314

Ielex 0046 12 104

FRANCE KONTRON S A France 6 Rue des Freres Caudron F 78140 Velizy Villacoublay Phone 00333 94 69 722 Telex 0042 695 672

ITALY

ELEDRA 3S S p A

Viale Elvezia 18

I 20154 Milano

Phone 0039 2 2349751

Telex 0043 314155

NETHERLANDS TEKELEC Airtronic Storkstraat 7 2700 AB Zoetermeer Phone 0031 79 310 100 Telex 0044 33 332

NORWAY VIKING MICROSYSTEMS A S N 1800 ASKIM Phone 0047 2 88 11 50 Telex 0056 11 502

SOUTH AFRICA BIOWAVE Electronics (PTY) Ltd PO Box 782 502 Sandton 2146 Johannesburg) Phone 0027 11 485805 Telex 4 24748 SA

SPAIN KONTRON S.A. Salvatierra 4 MADRID 34 Phone 0034 1 729 11 55 Telex 0058 23 382

SWEDEN TRANSFER AB Prastgardsg 9 or BOX 506 S 17229 Sundbyberg Phone 0046 8 9816 20 Telex 0054 19339

SWITZERLAND SWITZERLAND KONTRON ELECTRONIC AG Bernerstrasse Sud 169 CH 8048 Zurich Phone 0041 16 282 82 Telex 0045 \$2115

TITLE A

UNITED KINGDOM KONTRON

INSTRUMENTS LTD

Compact House

Campfield Road/

GB SI Albans AL1 5JG

Phone 0044 727 66222

Telex 0051 267102

UNITED STATES

KONTRON

ELECTRONIC INC

630 Price Ave

Redwood City CA 94063

Phone 001 415 361 1012

Telen 00255 910 378 5207