PMB HARDWARE MANUAL

03-3007-01 REV. A

3 October 1978

Price: \$4.50

03-3007-01

Revision A

Copyright © 1978 by Zilog, Inc. All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, electronic, mechanical, photocopying, recording, or otherwise, without the prior written permission of Zilog.

Zilog assumes no responsibility for the use of any circuitry other than circuitry embodied in a Zilog product. No other circuit patent licenses are implied.

# PMB USER'S GUIDE

# TABLE OF CONTENTS

| SECTION |            |                                                                       | PAGE       |

|---------|------------|-----------------------------------------------------------------------|------------|

| 1.0     | GENE       | RAL INFORMATION                                                       |            |

|         |            | Product Description                                                   |            |

| 2.0     | INST       | ALLATION                                                              |            |

|         | 2.1        |                                                                       | . 3        |

|         | 2.3        | Inspection                                                            |            |

|         | 2.4        | Power and Signal Connections                                          | . 4        |

| 3.0     | OPER       | NOITA                                                                 |            |

|         | 3.3<br>3.4 | PROM Type Selection  PROM Address Selection  I/O Address Modification | • 5<br>• 6 |

|         | 3.5        | PIO Input/Output Configuration                                        | . 10       |

| 4.0 | PROG                                   | RAMMING AND INITIALIZATION               |

|-----|----------------------------------------|------------------------------------------|

|     | 4.1<br>4.2<br>4.3<br>4.4               |                                          |

|     |                                        | Mode (PIO) 13                            |

|     | 4.5                                    | Setting the Interrupt Control Word (PIO) |

|     | 4.6<br>4.7                             | CTC Programming                          |

|     | 4.8                                    | Register (CTC)                           |

|     | 4.9                                    | Register (CTC)                           |

|     |                                        | Register (CTC)                           |

| 5.0 |                                        | DARD FACTORY STRAPPING IGURATION         |

|     | 5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6 | Component Carrier J2 25                  |

| 6.0 | TECH                                   | NICAL DESCRIPTION                        |

|     | 6.1<br>6.2                             | Detailed Description of                  |

|     | 6.3<br>6.4<br>6.5<br>6.6               | Assembly Drawings 39                     |

|     | 6.7                                    | Pin Out for PROM Memory Board 43         |

#### PMB USER'S MANUAL

SECTION 1: GENERAL INFORMATION

### 1.1 Product Description

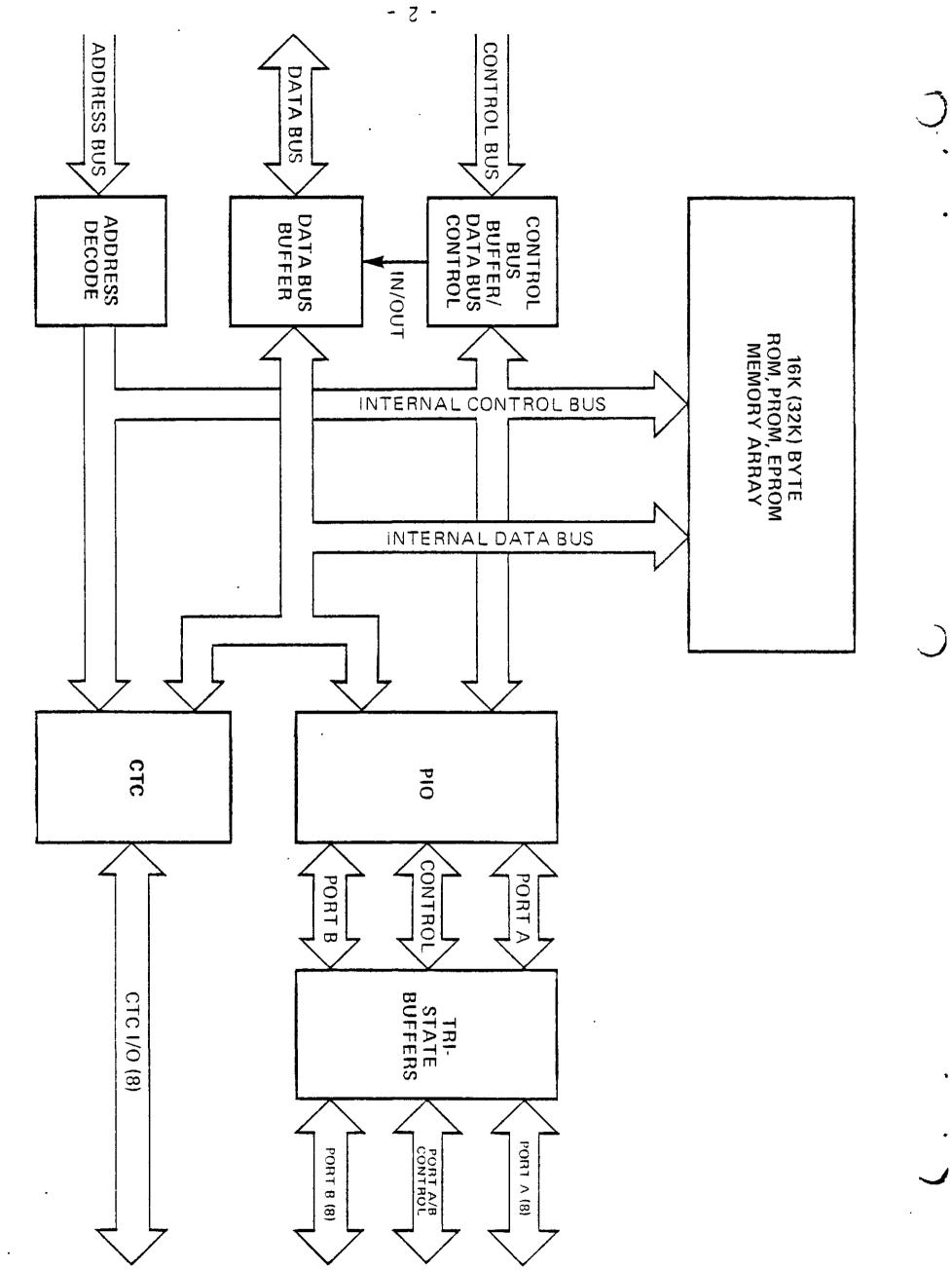

The Z80-PMB provides the Z80 Microcomputer Board Series with additional PROM or ROM memory and I/O capability.

The board contains sixteen, 24-pin sockets to accommodate up the 32K bytes of program memory using 2716 EPROMs or 2316 ROMs. The PMB will also accommodate 2708 EPROMs, or 6381 (82S181) PROMs for 16K bytes of program memory. Program memory addressing is implemented by using a PROM-based memory address decoder.

The PMB also contains a Z80-PIO and CTC providing 16 lines of parallel I/O with four control lines for byte operation, and four 8-bit counter/timers. The I/O devices are mapped anywhere into the I/O address space by strapping selections.

TO THE STATE OF TH

•

or interpret in Albert 400 is some of the party State to the south state to the south state to the south state to

The second of th

.

ŧ

e e de luga again de la de luga again de la de luga again de la de luga again de luga again de luga again de l

25 E247 St. A. T. 1996 F. 647

...

•

•

.

• -

**†**

1.2 BLOCK DIAGRAM

#### SECTION 2. INSTALLATION

#### 2.1 Introduction

The following section contains information on initial unpacking and inspection, power and signal connections to the MCB, and installation of the PME in the MCZ-l series systems.

## 2.2 Initial Unpacking and Inspection

Inspect the product for shipping damage as soon as it is unpacked. Check for any physical damage that may be attributed to abuse and handling during shipment. If the product is damaged in any way, notify the carrier immediately.

#### 2.3 Installation (MCZ-1)

The PMB may be installed in either of the prewired memory board positions in the MCZ-1/20 or MCZ-1/25 systems. These positions are J6 and J7 as described in the MCZ-1 Hardware User's Manual. In the MCZ-1/30 System, J6 and J7 of each card cage, may be used in the identical manner as previously described. In the MCZ-1/05, -1/10 and PDS, J1 (User's Option) and J4 (Video Display Board) will directly accommodate the PMB.

\*\* .;

## 2.4 Power and Signal Connections

The Z80-PMB is pin-compatible with the Z80 MCB bus structure. For convenience, the wire list for interconnection between the MCB and the PROM Memory Board is provided:

| TO .                                                                                                             | FROM                                                                                                                                                                                                     | DESCRIPTION                                                                                                                                                                                                                                                                                                                                    |

|------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PME:1-3, 59-61 PME:4 PMB:5 PME:7 PMB:8 PMB:12 PME:13 PME:26 PME:27 PMB:29 PMB:30 PMB:30 PMB:37 Next IEI Next IEI | MCB:1-3, 59-61<br>MCB:4<br>MCB:5<br>Last used IEO<br>MCB:8<br>MCB:12<br>MCB:13<br>MCB:26<br>MCB:27<br>MCB:29<br>MCB:30<br>MCB:30<br>MCB:32<br>MCB:36<br>MCB:37<br>PMB:50<br>PMB:58<br>MCB:62-64, 120-122 | +5V P.S. IORQ- DATA BIT (5) IEI of PIO DATA BIT (3) DATA BIT (6) DATA BIT (0) ADDR. BIT (7) ADDR. BIT (8) ADDR. BIT (5) ADDR. BIT (15) ADDR. BIT (15) ADDR. BIT (11) IEO of PIO IEO of CTC CCMMOM -5V P.S. DATA BIT (4) +12V P.S. DATA BIT (2) DATA BIT (7) DATA BIT (1) INT- MRQ- ADDR. BIT (10) ADDR. BIT (10) ADDR. BIT (14) ADDR. BIT (12) |

| PMB:117                                                                                                          | MCB:83                                                                                                                                                                                                   | ROM DISABLE-                                                                                                                                                                                                                                                                                                                                   |

TABLE 2.3.1: MCB TO PMB WIRE LIST

### SECTION 3: OPERATION

#### 3.1 Introduction

This section contains a general description of the PROM Memory Board's operation, and provides some application software for initializing and communicating to the PIO and CTC.

## 3.2 PROM Type Selection

Jumper area J3 is used to configure the PMB for a particular type of PROM. The following table shows the pin assignments which differ between the three PMB-compatible PRCMs:

| Pin | 2708 | 2716   | 6381 | (825181) |

|-----|------|--------|------|----------|

| 18  | PRGM | PD/PGM | •    | CE4      |

| 19  | VDD  | A10    |      | CE3      |

| 21  | VBB  | VPP    |      | CEl-     |

For a 2708, the following jumpers are to be connected at J3:

```

J3-1 to J3-16 PRGM = GND

J3-2 to J3-15 Disable Bank A during Bank B access

J3-3 to J3-14 Disable Bank B for lower lK of 2K page

J3-4 to J3-13 VDD = +12V

J3-7 to J3-10 VBB = -5V

```

For a 2716 and (2316), the following jumpers are to be connected at J3:

```

J3-1 to J3-16 PD/PGM = GND J3-3 to J3-13 Al0 = IAB10 J3-6 to J3-11 VPP = +5V

```

For a 6381, the following jumpers are to be connected at J3:

```

J3-2 to J3-15 Disable Bank A during Bank B access J3-3 to J3-14 Disable Bank B for lower lK of 2K page J3-5 to J3-12 CE3 = +5V J3-5 to J3-16 CE4 = +5V J3-8 to J3-10 CE1- = GND

```

#### 3.3 PROM Address Selection

PROM address selection is accomplished by programming particular bit maps into the decoder PROMs AlO and All. Inputs to the decoder PROMs are IAB15-IAB11, which address the 32 PROM locations. Each of the 32 PROM locations represents a 2K byte segment of memory space. To place a PROM in a particular 2K segment, program the appropriate data byte at the address corresponding to the desired 2K segment. See Figure 3.3.1 for the data bytes associated with each PROM socket, and Figure 3.3.2 for the correspondence between 2K memory segments and control PROM locations. Unused locations in the address decoder PROMs, AlO and All, should be programmed with OFFH. The following two examples illustrate the address selection procedure:

Example 1 - Assume that two 2716's are to be used, one located at 0 to 7FFH, and the other at F800H to FFFFH. Also assume that the 2716's are placed in PROM sockets 0 (A24) and 15 (A22), respectively. Decoder PROM AlO should enable PROM socket 0 (A24) when the addresses 0 to 7FFH are being accessed. For this address range, Figure 3.3.2 shows that address 0 in the decoder PROM should be programmed. Figure 3.3.1 shows that the data byte corresponding to PRCM socket 0 (A24) is OFEH. Therefore, data byte OFEH should be programmed into address 0 of AlO. Decoder PROM All should enable PROM socket 15 (A22) when the addresses F800H to FFFFH are being accessed. Again, using Figures 3.3.1 and 3.3.2, data byte 07FH should be programmed into address 1FH of All.

Example 2 - The above example is now repeated using 2708's. The PROM select logic is such that when using 1K PROMs, the least significant Kbyte of a 2K byte page resides in PROM Bank A. The most significant Kbyte resides in the corresponding socket in PROM Bank B. Shown below is the correspondence between PROM sockets and memory segments. For this example:

| PROM SOCKET | MEMORY SEGMENT |

|-------------|----------------|

| 0 (A24)     | 0 to 3FFH      |

| 8 (A15)     | 400H to 7FFH   |

| 7 (A31)     | F800H to F3FFH |

| 15 (A22)    | FC00H to FFFFH |

Using Figures 3.3.1 and 3.3.2, it can be seen that data bytes FEH and 7FH should be programmed into locations 0 and 1FH, respectively, in both AlO and All.

| PF               | ROM SO                                    | CKI | ΞT                  |                                  | * | DATA BYTE TO BE PROGRAMMED INTO Al0 OR All |

|------------------|-------------------------------------------|-----|---------------------|----------------------------------|---|--------------------------------------------|

| 1<br>2<br>3<br>4 | (A24)<br>(A25)<br>(A26)<br>(A27)<br>(A28) | ,   | 9<br>10<br>11<br>12 | (A16)<br>(A17)<br>(A18)<br>(A19) | • | 0FEH<br>0FDH<br>0FBH<br>0F7H<br>0EFH       |

|                  | (A29)<br>(A30)                            | ,   | 14                  | (A21)                            |   | ODFH<br>OBFH                               |

| /                | (A31)                                     | ,   | T )                 | (A22)                            |   | 07FH                                       |

FIGURE 3.3.1: PROM ENABLE PROGRAMMING

## LOCATION TO BE PROGRAMMED IN AlO OR All

| MEMORY SEGMENT                                                                                                                                                                                                                                                                                                           | IN AlO OR All     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| MEMORY SEGMENT  0000-07FFH 0800-0FFFH 1000-17FFH 1800-1FFFH 2000-27FFH 2800-2FFFH 3000-37FFH 3800-3FFFH 4000-47FFH 4800-4FFFH 5000-57FFH 5800-5FFFH 6800-6FFFH 7000-77FFH 7800-7FFFH 8800-8FFFH 9000-97FFH 8800-8FFFH 9800-9FFFH A000-A7FFH A800-AFFFH B800-BFFFH C000-C7FFH C800-CFFFH C800-CFFFH D800-DFFFH E800-EFFFH |                   |

| F000-F7FFH<br>F800-FFFFH                                                                                                                                                                                                                                                                                                 | 1DH<br>1EH<br>1FH |

|                                                                                                                                                                                                                                                                                                                          |                   |

FIGURE 3.3.2: PROM ENABLE ADDRESS MAPPING

#### 3.4 I/O Address Modification

Jumper areas Jl and J2 are used to assign I/O port addresses to the CTC and PIO. These two devices have the following ports which are addressed in the order indicated:

| PIO | DATA POR | RT A |   | 0 |

|-----|----------|------|---|---|

| PIO | DATA POF | RT B |   | 1 |

| PIO | CONTROL  | PORT | A | 2 |

| PIO | CONTROL  | PORT | В | 3 |

|     |          |      |   |   |

| CTC | CHANNEL  | 0    |   | 0 |

| CTC | CHANNEL  | 1    |   | 1 |

| CTC | CHANNEL  | 2    |   | 2 |

| CTC | CHANNEL  | 3    |   | 3 |

Jumper area J2 selects into which range of 32 I/O ports the above eight ports will be located. See Figure 3.4.1 for the possible jumper selections for J2. Once the port range has been established, jumper area J1 is used to position the two groups of four ports at specific locations within the range. See Figure 3.4.2 for the possible jumper selections for J1.

For example, assume that the four PIO ports are to be 6CH, 6DH, 6EH, and 6FH, and that the four CTC ports are to be 74H, 75H, 76H, and 77H. All of these ports are in the range of 60-7FH. Figure 3.4.1 shows that the following jumpers at J2 are to be connected:

J2- 9 to J2-7 J2-10 to J2-4 J2-11 to J2-2

Within this range, the four PIO ports are located from OCH to OFH. Figure 3.4.2 shows that jumper J1-13 to J1-5 should be connected. The four CTC ports are located from 14H to 17H within the range 60-70H. Therefore, a jumper is connected from J1-14 to J1-7.

| J2-9                                                 | J2-10                                                | J2-11                                                | I/O PORT RANGE                                                              |

|------------------------------------------------------|------------------------------------------------------|------------------------------------------------------|-----------------------------------------------------------------------------|

| TO                                                   | TO                                                   | ТО                                                   |                                                                             |

| J2-7<br>J2-7<br>J2-7<br>J2-6<br>J2-6<br>J2-6<br>J2-6 | J2-5<br>J2-5<br>J2-4<br>J2-5<br>J2-5<br>J2-4<br>J2-4 | J2-3<br>J2-2<br>J2-3<br>J2-3<br>J2-2<br>J2-3<br>J2-2 | 0-1FH<br>20-3FH<br>40-5FH<br>60-7FH<br>80-9FH<br>A0-BFH<br>C0-DFH<br>E0-FFH |

FIGURE 3.4.1: I/O PORT ADDRESS RANGE

| JUMPER CONNECTION       | FOUR PORTS WITHIN |

|-------------------------|-------------------|

| TO J13(PIO) OR J14(CTC) | 32-PORT RANGE     |

|                         |                   |

| J1-2                    | OH to 3H          |

| J1-3                    | 4H to 7H          |

| J1-4                    | 8H to OBH         |

| J1-5                    | OCH to OFH        |

| J1-6                    | 10H to 13H        |

| J1-7                    | 14H to 17H        |

| J1-8                    | 18H to 1BH        |

| J1-9                    | 1CH to 1FH        |

FIGURE 3.4.2: PORT GROUP ADDRESS ASSIGNMENT

## 3.5 PIO Input/Output Configuration

Each of the PIO ports A and B may be configured for input or output.

When Port A is used as an input port, jumpers are to be connected at Kl as shown in Table 3.5.1. The bus drivers A5, A6, and A7 should either be disabled or removed. (Note that A6 and A7 are also used for Port B.) The termination resistors may also be installed, depending on the application. In the output mode, the jumpers at Kl are removed, and the bus drivers are enabled.

When Port B is used as an input port, jumpers are to be connected at K2, as shown in Table 3.5.2. As with Port A, the appropriate bus drivers must be disabled or removed. The termination resistor network, Al2, may also be installed. In the output mode, the jumpers at K2 are removed, and the bus drivers are enabled.

| Conne   | ction   | Signal    |

|---------|---------|-----------|

| K1-5    | to Kl-6 | Ã0        |

| K1-10   | K1-9    | A1        |

| K1 - 11 | K1-7    | A2        |

| K1-12   | K1-8    | <b>A3</b> |

| K1-13   | K1-1    | A4        |

| K1-14   | K1-2    | A5        |

| Kl-15   | K1-3    | A6        |

| Kl-16   | K1-4    | A7        |

TABLE 3.5.1 PIO PORT A JUMPER

| Conn   | ection   | Signal    |

|--------|----------|-----------|

| K2-1   | to K2-16 | В0        |

| K2-2   | K2-15    | Bl        |

| K2 - 3 | K2-14    | В2        |

| K2-4   | K2-13    | <b>B3</b> |

| K2-5   | K2-12    | B4        |

| K2-6   | K2-11    | B5        |

| K2 - 7 | K2-10    | B6        |

| K2-8   | K2-9     | В7        |

|        |          |           |

TABLE 3.5.2 PIC PORT B JUMPER

## SECTION 4: PROGRAMMING AND INITIALIZATION

#### 4.1 Introduction

The following section contains information and programming examples for on-board PIO and CTC operation.

#### 4.2 Reset (PIO)

The Z80-PIO automatically enters a reset state when power is applied. The reset state performs the following functions:

- o Both port mask registers are reset to inhibit all port data bits.

- o Port data bus lines are set to a high impedance state and the Ready 'handshake' signals are inactive (low). Mode l is automatically selected.

- o The vector address registers are not reset.

- o Both port interrupt enable flip flops are reset.

- o Both port output registers are reset.

In addition to the automatic power-on reset, the PIO can be reset by applying an Ml- signal without the presence of a RD- or IORQ- signal. If no RD- or IORQ- is detected during Ml-, the PIO- will enter the reset state immediately after the Ml- signal goes inactive. The purpose of this reset is to allow a single external gate to generate a reset without a power down sequence. This approach was required due to the 40-pin packaging limitation.

Once the PIO has entered the internal reset state, it is held there until the PIO receives a control word from the CPU.

### 4.3 Loading the Interrupt Vector (PIO)

The PIO has been designed to operate with the Z80-CPU using the mode 2 interrupt response. This mode requires that an interrupt vector be supplied by the interrupting device. This vector is used by the CPU to form the address for the interrupt service routine of that port. This vector is placed on the Z-80 data bus during an interrupt acknowledge

cycle by the highest priority device requesting service at that time. (Refer to the Z80-CPU Technical Manual for details on how an interrupt is serviced by the CPU.) The desired interrupt vector is loaded into the PIO by writing a control word to the desired port of the PIO with the following format:

| D7 | D6 | D5 | D4 | D3 | D2 | Dl | DO |

|----|----|----|----|----|----|----|----|

| V7 | V6 | V5 | V4 | V3 | V2 | V1 | 0* |

<sup>\*</sup> Signifies this control word is an interrupt vector

DO is used in this case as a flag bit which, when low, causes V7 through V1 to be loaded into the vector register. At interrupt acknowledge time, the vector of the interrupting port will appear on the Z-80 data bus exactly as shown in the format above.

## 4.4 Selecting an Operating Mode (PIO)

Port A of the PIO may be operated in any of four distinct modes: Mode 0 (output mode), Mode 1 (input mode), Mode 2 (bidirectional mode), and Mode 3 (control mode). Note that the mode numbers have been selected for mnemonic significance; i.e., 0=Out, 1=In, 2=Bidirectional. Port B can operate in any of these modes except Mode 2.

The mode of operation must be established by writing a control word to the PIO in the following format:

| D7   | D6   | D5    | D4  | D-3            | D2 | Dl      | D0 |

|------|------|-------|-----|----------------|----|---------|----|

| M1   | MO   | X     | X   | 1,             | 1  | 1       | 1  |

| mode | word | not u | seđ | signi<br>to be |    | node wo | rd |

Bits D7 and D6 form the binary code for the desired mode according to the following table:

| D7 | D6 | Mode              |

|----|----|-------------------|

| 0  | 0  | 0 (output)        |

| 0  | 1  | l (input)         |

| 1  | 0  | 2 (bidirectional) |

| 1  | 1  | 3 (control)       |

Bits D5 and D4 are ignored. Bits D3-D0 must be set to 1111 to indicate "Set Mode".

Selecting Mode O enables any data written to the port output register by the CPU to be enabled onto the port data bus. The contents of the output register may be changed at any time by the CPU simply by writing a new data word to the port. Also, the current contents of the output register may be read back to the Z80-CPU at any time through the execution of an input instruction.

With Mode O active, a data write from the CPU causes the Ready handshake line of that port to go high to notify the peripheral that data is available. This signal remains high until a strobe is received from the peripheral. The rising edge of the strobe generates an interrupt (if it has been enabled) and causes the Ready line to go inactive. This very simple handshake is similar to that used in many peripheral devices.

Selecting Mode I puts the port into the input mode. To start handshake operation, the CPU merely performs an input read operation from the port. This activates the Ready line to the peripheral to signify that data should be loaded into the empty input register. The peripheral device then strobes data into the port input register using the strobe line. Again, the rising edge of the strobe causes an interrupt request (if it has been enabled) and deactivates the Ready signal. Data may be strobed into the input register regardless of the state of the Ready signal if care is taken to prevent a data overrun condition.

Mode 2 is a bidirectional data transfer mode which uses all four handshake lines. Therefore, only Port A may be used for Mode 2 operation. Mode 2 operation uses the Port A handshake signals for output control and the Port B handshake signals for input control. Thus, both A RDY and B RDY may be active simultaneously. The only operational difference between Mode

O and the output portion of Mode 2 is that data from the Port A output register is allowed on to the port data bus only when A STB- is active in order to achieve a birdirectional capabilty.

Mode 3 operation is intended for status and control applications and does not utilize the handshake signals. When Mode 3 is selected, the next control word sent to the PIO must define which of the port data bus lines are to be inputs and which are outputs. The format of the control word is shown below:

D7 D6 D5 **D4 D3** D2 D1 D0

I/O7 I/O6 I/O5 I/O4 I/O3 I/O2 I/O1 I/O0

If any bit is set to a one, then the corresponding data bus line will be used as an input. Conversely, if the bit is reset, the line will be used an an output.

During Mode 3 operation, the strobe signal is ignored and the Ready line is held low. Data may be written to a port or read from a port by the Z80-CPU at any time during Mode 3 operation. When reading a port, the data returned to the CPU will be composed of input data from port data bus lines assigned as inputs plus port output register data from those lines assigned as outputs.

## 4.5 Setting the Interrupt Control Word (PIO)

The interrupt control word for each port has the following format:

D7 D6 D5 D4 D3 D2 Dl D0Enable AND/ High/ 1 Masks 0 1 1 OR Low follows Interrupt used in Mode 3 only signifies interrupt control word

If bit D7=1, the interrupt enable flip flop of the port is set and the port may generate an interrupt. If bit D7=0, the enable flag is reset and interrupts may not be generated. an interrupt is pending when the enable flag is set, it will then be enabled onto the CPU interrupt request line. D6, D5, and D4 are used only with Mode 3 operation. setting bit D4 of the interrupt control word during any mode of operation will cause any pending interrupt to be reset. These three bits are used to allow for interrupt operation in Mode 3 when any group of the I/O lines go to certain defined states. Bit D6 (AND/OR) defines the logical operation to be performed in port monitoring. If bit D6=1, an AND function is specified, and if D6=0, an OR function is specified. example, if the AND function is specified, all bits must go to a specified state before an interrupt will be generated, while the OR function will generate an interrupt if any specified bit goes to the active state.

Bit D5 defines the active polarity of the port data bus line to be monitored. If bit D5=1, the port data lines are monitored for a high state while if D5=0, they will be monitored for a low state.

If bit  $\mathbb{C}4=1$ , the next control word sent to the PIO must define a mask as follows:

| D7  | D6  | D5  | D4  | D3  | D2  | Dl  | D0  |

|-----|-----|-----|-----|-----|-----|-----|-----|

| MB7 | MB6 | MR5 | MR4 | MB3 | MB2 | MR1 | MRO |

Only those port lines whose mask bit is zero will be monitored for generating an interrupt.

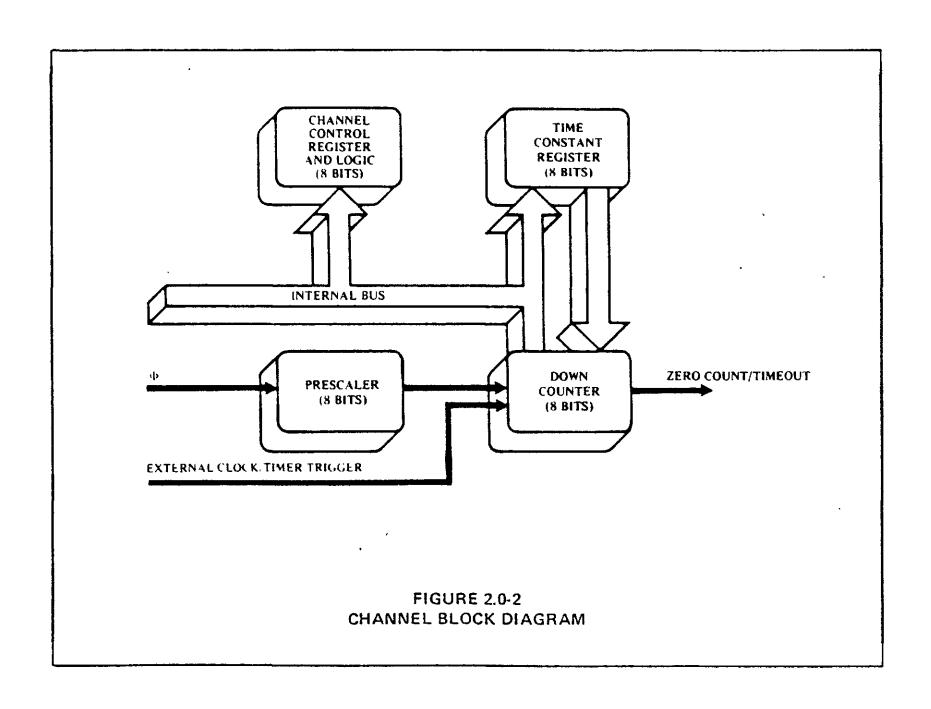

## 4.6 CTC Programming

Pefore a Z80-CTC channel can begin counting or timing operations, a Channel Control Word and a Time Constant data word must be written to it by the CPU. These words will be stored in the Channel Control Register and the Time Constant Register of that channel. In addition, if any of the four channels have been programmed with bit 7 of their Channel Control Words to enable interrupts, an Interrupt Vector must be written to the appropriate register in the CTC. Due to automatic features in the Interrupt Control Logic, one pre-programmed Interrupt Vector suffices for all four channels.

## 4.7 Loading the Channel Control Register (CTC)

To load a Channel Control Word, the CPU performs a normal I/O Write sequence to the port address corresponding to the desired CTC channel. Two CTC input pins, namely CSO and CSl, are used to form a 2-bit binary address to select one of four channels within the device. In many system architectures, these two input pins are connected to Address Bus lines AC and Al, respectively, so that the four channels in a CTC device will occupy contiguous I/O port addresses. A word written to a CTC channel will be interpreted as a Channel Control Word, and loaded into the Channel Control Register, its bit O is a logic 1. The other seven bits of this word select operating modes and conditions as indicated in Figure 4.9.1.

D7. D6 D5 D4 D3 D2 Dl D0INTERRUPT LOAD ENABLE TIME 1 MODE RANGE SLOPE TRIGGER RESET CONSTANT

NOTE: RANGE and TRIGGER used in Timer Mode only

#### Bit 7=1

The channel is enabled to generate an interrupt request sequence every time the Down Counter reaches a zero-count condition. To set this bit to 1 in any of the four Channel Control Registers necessitates that an Interrupt Vector also be written to the CTC before operation begins. Channel interrupts may be programmed in either Counter Mode or Timer Mode. If an updated Channel Control Word is written to a channel already in operation, with bit 7 set, the interrupt enable selection will not be retroactive to a preceding zero-count condition.

#### Bit 7=0

Channel interrupts disabled.

#### Bit 6=1

Counter Mode selected. The Down Counter is decremented by each triggering edge of the External Clock (CLK/TRG) input. The Prescaler is not used.

Bit 6=0

Timer Mode selected. The Prescaler is clocked by the System Clock  $\Phi$ , and the output of the Prescaler, in turn, clocks the Down Counter. The output of the Down Counter (the channel's ZC/TO output) is a uniform pulse train of periods given by the product

t \*P\*TC

where t is the period of System Clock  $\Phi$ , P is the Prescaler factor of 16 or 256, and TC is the time constant data word.

Bit 5=1

(Defined for Timer Mode only.) Prescaler factor is 256.

Bit 5=0

(Defined for Timer Mode only.) Prescaler factor is 16.

Bit 4=1

TIMER MODE - positive edge trigger starts timer operation. COUNTER MODE - positive edge decrements the down counter.

#### Bit 4=0

TIMER MODE - negative edge trigger starts timer operation. COUNTER MODE - negative edge decrements the down counter.

#### Bit 3=1

Timer Mode only - External trigger is valid for starting timer operation after rising edge of T2 of the machine cycle following the one that loads the time constant. The Prescaler is decremented 2 clock cycles later if the setup time is met, otherwise, 3 clock cycles.

#### Bit 3=0

Timer Mode only - Timer begins operation on the rising edge of T2 of the machine cycle following the one that loads the time constant.

#### Bit 2=1

The time constant data word for the Time Constant Register will be the next word written to this channel. If an updated Channel Control Word and time constant data word are written to a channel while it is already in operation, the Down Counter will continue dcrementing to zero before the new time constant is loaded into it.

#### Bit 2=0

No time constant data word for the Time Constant Register should be expected to follow. To program bit 2 to this state implies that this Channel Control Word is intended to update the status of a channel already in operation, since a channel will not operate without a correctly programmed data word in the Time Constant Register, and a set bit 2 in this Channel Control Word provides the only way of writing to the Time Constant Register.

#### Bit 1=1

Reset channel. Channel stops counting or timing. This is not a stored condition. Upon writing into this bit, a reset pulse discontinues current channel operation, however, none of the bits in the channel control register are changed. If both bit 2=1 and bit l=1, the channel will resume operation upon loading a time constant.

Pit 1=0

Channel continues current operation.

## 4.8 Loading the Time Constant Register (CTC) ---

A channel may not begin operation in either Timer Mode or Counter Mode unless a time constant data word is written into the Time Constant Register by the CPU. This data word will be expected on the next I/O Write to this channel following the I/O Write of the Channel Control Word, provided that bit 2 of the Channel Control Word is set. The time constant data word may be any integer value in the range 1-256. If all eight bits in this word are zero, it is interpreted as 256. If a time constant data word is loaded to a channel already in operation, the Down Counter will continue decrementing to zero before the new time constant is loaded from the Time Constant Register to the Down Counter.

#### TIME CONSTANT REGISTER

| D7  | D6  | D5  | D4  | . D3 | D2  | Dl  | D0 ~ | اسعد |

|-----|-----|-----|-----|------|-----|-----|------|------|

| TC7 | TC6 | TC5 | TC4 | TC3  | TC2 | TCl | TCO  |      |

| MSB |     |     |     |      |     |     | LSB  |      |

Figure 4.9.1: Channel Block Diagram

## 4.9 Loading the Interrupt Vector Register (CTC)

The Z80-CTC has been designed to operate with the Z80-CPU programmed for Mode 2 interrupt response. Under the requirements of this mode, when a CTC channel requests an interrupt and is acknowledged, a 16-bit pointer must be formed to obtain a corresponding interrupt service routine starting address from a table in memory. The upper 8 bits of this pointer are provided by the CPU's I register, and the lower 8 bits of the pointer are provided by the CTC in the form of an Interrupt Vector unique to the particular channel that requested the interrupt.

## MODE 2 INTERRUPT CPERATION

INTERRUPT

SERVICE

ROUTINE

STARTING

ADDRESS

TABLE

Desired starting address

pointed to by:

I REG 7 BITS FROM 0

CONTENTS PERIPHERAL

The high order 5 bits of this Interrupt Vector must be written to the CTC in advance as part of the initial programming sequence. To do so, the CPU must write to the I/O port address corresponding to the CTC channel 0, just as it would if a Channel Control Word were being written to that channel, except that bit 0 of the word being written must contain an 0. (As explained above in Section 4.7, if bit 0 of a word written to a channel were set to 1, the word would be interpreted as a Channel Control Word, so a 0 in bit 0 signals the CTC to load the incoming word into the Interrupt Vector Register.) Bits 1 and 2, however, are not used when loading this vector. At the time when the interrupting channel must place the interrupt Vector on the Z80 Data Bus, the Interrupt Control Logic of the CTC automatically supplies a binary code in bits 1 and 2 identifying which of the four CTC channels is to be serviced.

## INTERRUPT VECTOR REGISTER

# Interrupt Vector Register

| D7  | D6    | D5     | D4  | D3  | D2          | Dl | D0                                                                          |  |

|-----|-------|--------|-----|-----|-------------|----|-----------------------------------------------------------------------------|--|

| V7  | V6    | V5     | V 4 | V 3 | X           | X  | 0                                                                           |  |

| SUP | PLIED | BY USE | R   |     | 0<br>0<br>1 | 1  | CHANNEL 0 (Highest Priority CHANNEL 1 CHANNEL 2 CHANNEL 3 (Lowest Priority) |  |

Automaticallly inserted by Z80-CTC

#### SECTION 5: STANDARD FACTORY STRAPPING CONFIGURATION

#### 5.1 Introduction

The following sections show how the PIO and CTC port address component carriers are strapped as provided by Zilog. All other required component carriers are provided but are left unstrapped.

## 5.2 Component Carrier Jl

Component carrier Jl (Part No. 33-0173-17) for PIO and CTC port selects: (This part should be supplied with the board)

$$J1-13$$

TO  $J1-2$  PIO = 0, 1, 2, 3

$J1-14$  J1-2 CTC=4, 5, 6, 7

## 5.3 Component Carrier J2

Component carrier J2 (Part No. 33-0173-18) for I/O port range select: (This part should be supplied with the board) (PIO ports begin at AOH)

#### 5.4 Component Carrier J3

Component carrier J3 to select 2708 PROMS:

| J3-1 | TO | J3-16 |

|------|----|-------|

| J3-2 |    | J3-15 |

| J3-3 |    | J3-14 |

| J3-4 |    | J3-13 |

| J3-7 |    | J3-10 |

# 5.5 Component Carrier Kl

Component carrier Kl to configure PIO port A I/O lines.

| Kl-1   | ${	t TO}$ | Kl-13   |

|--------|-----------|---------|

| K1-2   |           | K1 - 14 |

| K1 - 3 |           | K1-15   |

| Kl-4   |           | K1-16   |

| K1-5   |           | K1-6    |

| Kl-7   |           | K1-11   |

| Kl-8   |           | K1-12   |

| K1-9   |           | K1 - 10 |

|        |           |         |

# 5.6 Component Carrier K2

Component Carrier K2 to configure PIO port I/O lines:

| K2-1   | TO | K2-16   |

|--------|----|---------|

| K2-2   |    | K2-15   |

| K2-3   |    | K2-14   |

| K2 - 4 |    | K2 - 13 |

| K2 - 5 |    | K2-12   |

| K2-6   |    | K2-11   |

| K2 - 7 |    | K2-10   |

| K2 - 8 |    | K2-9    |

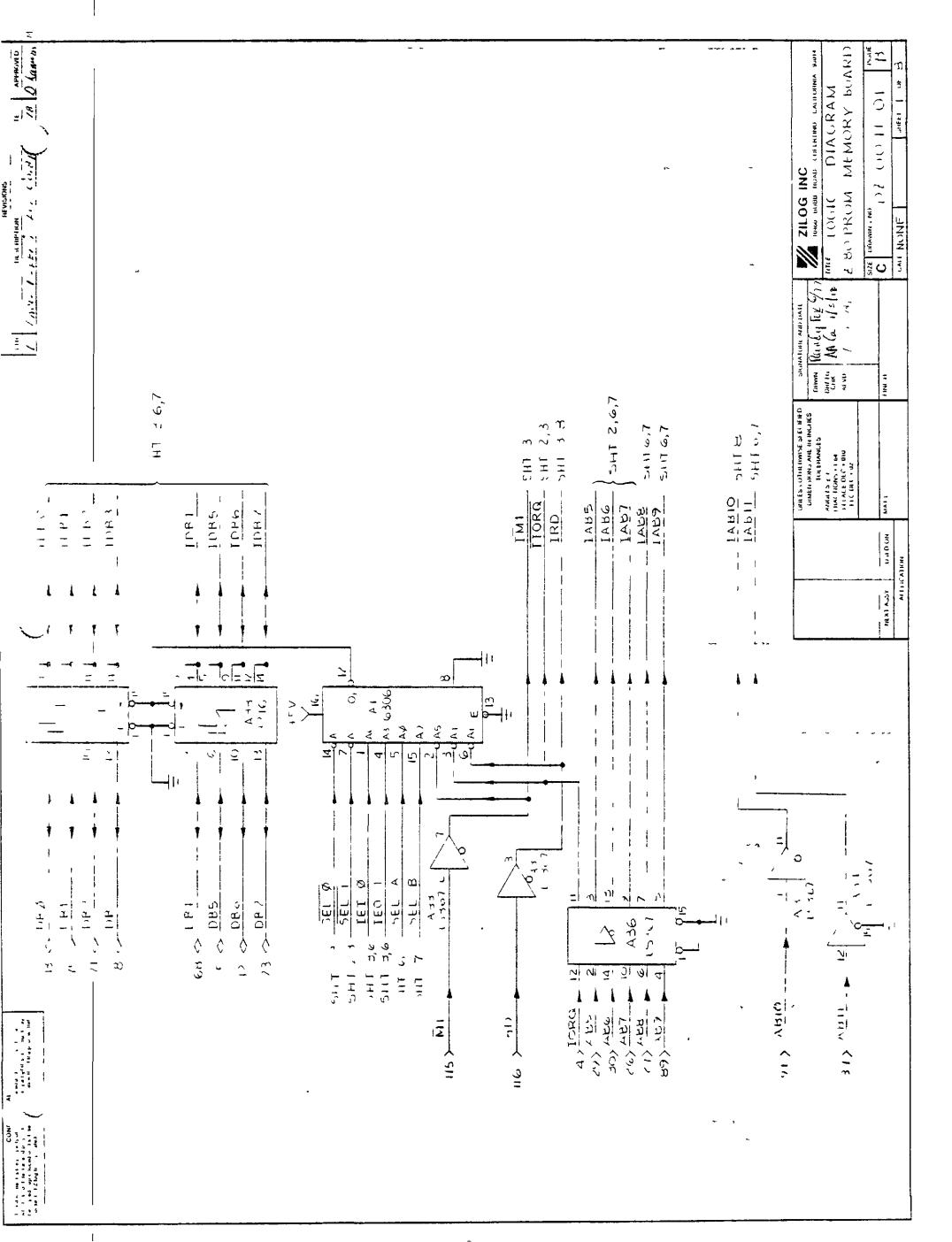

## SECTION 6. TECHNICAL DESCRIPTION

#### 6.1 Introduction

The following section contains a detailed description of the operation and logical throughput of the PMB. The reader is directed to use the accompanying schematic at the end of the manual as a reference. The board's specification is also included in this section.

## 6.2 Detailed Description of Board Schematics

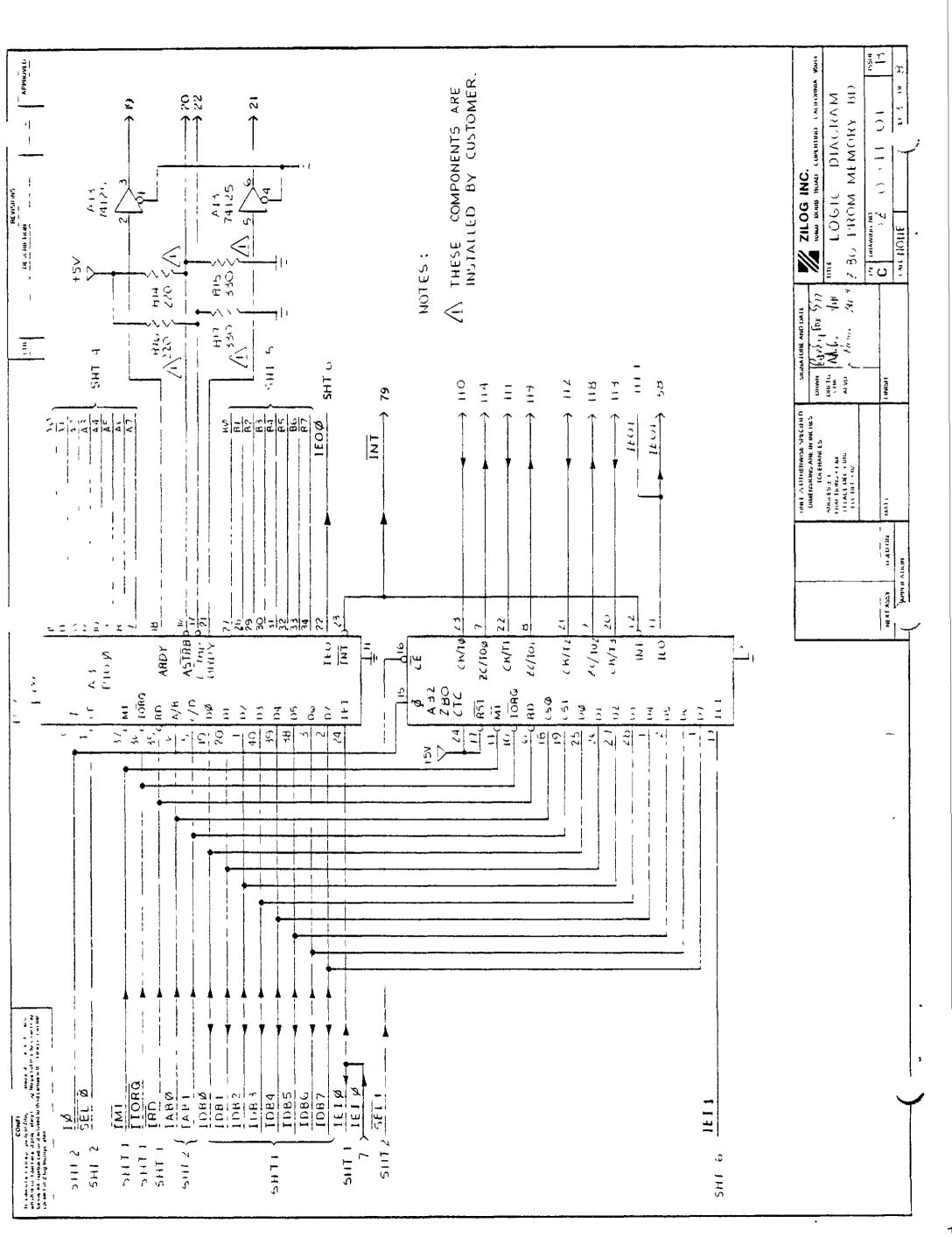

#### Sheet 1

Sheet I consists of the bi-directional data bus buffers, through which data bytes pass between the system data bus and the PMB internal data bus. The direction of the buffers is determined by control PROM Al whose bit map is shown in Figure 6.2.1. Some address and control lines buffers are also included on this sheet.

化二甲烷基二甲烷 斯塞尔 人名德内尔尔尔 化二氯二甲烷二甲烷异苯基

FF 000 FF FF FF FFFF FF 010 FF FΕ FF FFFFFEFFFF FFFEFFFFFEFFFFFF020 FF FF FF FF FEFE FF FF FF FF FF FE FE FF $\mathbf{F}\mathbf{F}$ 030 FF FE FF FFFFFE FF FFFFFΕ FFFFFFFE FFFF 040 FE FEFEFEFEFEFF FF FEFΕ FFFF FF FF FFFF050 FF FE FF FF FF FE FF FF FF FE FF FFFEFFFF060 FF FF FF FFFEFΕ FFFFFF FFFF FF FΕ FE FF FF 070 FF FE FF FF FF FE FF FFFFFE FF FF FF FE FFFF 080 FF FF FFFFFF FF FFFF FF FF FFFFFF FFFF 090 FE FF FE FF FΕ FF FFFF FFFFFF FFFF $\Gamma \Gamma$ FF FF FF OAO FF FF FFFFFE FE FF FFFFFFFE FF FEFF FF OBO FE FF FF FF FE FF FF FF FE FF FFFF FE FF FF FF FF OCO FE FE FE FE FE FE FΕ FFFΕ FF FFFF FF FF ODO FE FF FF FF FE FF FF FF FE FF FFFFFE FFFF FFOEO FF FF FF FF FE FE FF FFFF FF FFFFFEFE FFFF FE FF FF OFO FE FF FF FF FF FE FF FFFFFEFF FF FF FF 100 FF FF FF FF FF FFFFFF FFFF FF FFFF 110 FF FE FF FF FF FE FF FFFF FE FFFFFF FE FF FF FF FF FF FF FE FF 120 FE FE FF FF FF FF FFFFFF FF FE FF FF 130 FF FΕ FFFFFFFFFEFFFFFFFE FF 140 FE FE FE FE FE FE FE FΕ FF FF FFFF FF FF FF FF 150 FF FE FF FF FF FE FF FF FF FE FF FFFFFE FF FF160 FE FE FF FF FFFF FF FF FE FE FF FF FFFF FFFF 170 FF FE FF FF FFFE FF FFFFFE FFFF FF FE FF FF180 FF FF FF FFFFFF FF FFFF FF FFFFFFFFFFFF 190 FE FF FF FF FE FF FF FF FE FF FFFFFΕ FF FFFF FF1AO FE FEFFFFFF FF FF FF FE FE FFFF FF 1BO FE FF FF FF FE FF FFFE FF FFFF FFFEFFFFFF 1CO FE FE FE FEFE FE FΕ FE FFFF FFFFFF FF FF 1D0 FE FF FF FFFE FF FFFF FE FF FF FFFE FF FFFF 1EO FE FE FF FF FF FF FF FE FE FF FF FF FF FF FFFF1FO PE FF FF FF FE FF FF FF FE FF FF FF FE FF

Figure 6.2.1. BIT MAP FOR DATA BUS CONTROL PROM

#### Sheet 2

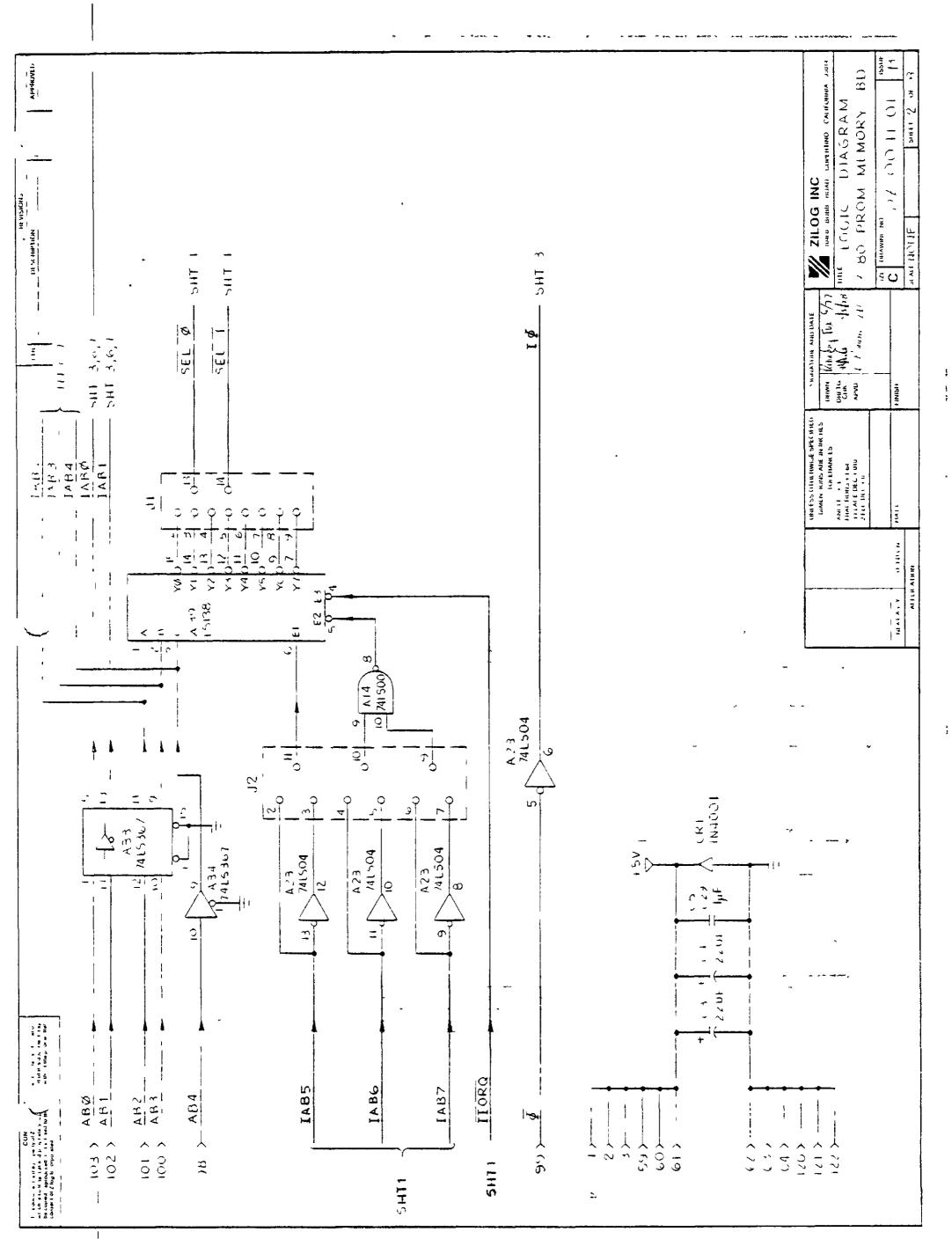

The I/O port select logic for the CTC and PIO is shown on Sheet 2. Jumper area J2 selects one out of eight possible I/O groups, with each group consisting of 32 I/O port addresses. Jumper area J1 is used to located the CTC and PIO ports within the group selected by J2. The two least significant address bits determine which one of the four I/O ports is being addressed in either the PIO or CTC.

### Sheet 3

Sheet 3 contains the Z80-PIC and Z80-CTC. They both communicate with the Z80-CPU via the PMB internal data and control busses. The clock/trigger inputs and zero count/time out outputs of the CTC are brought to the PMB card edge connector. The I/O lines of the PIO are connected to a jumper/buffer area shown on Sheets 4 and 5. Interrupts are daisy-chained such that PIO interrupts have priority over those of the CTC.

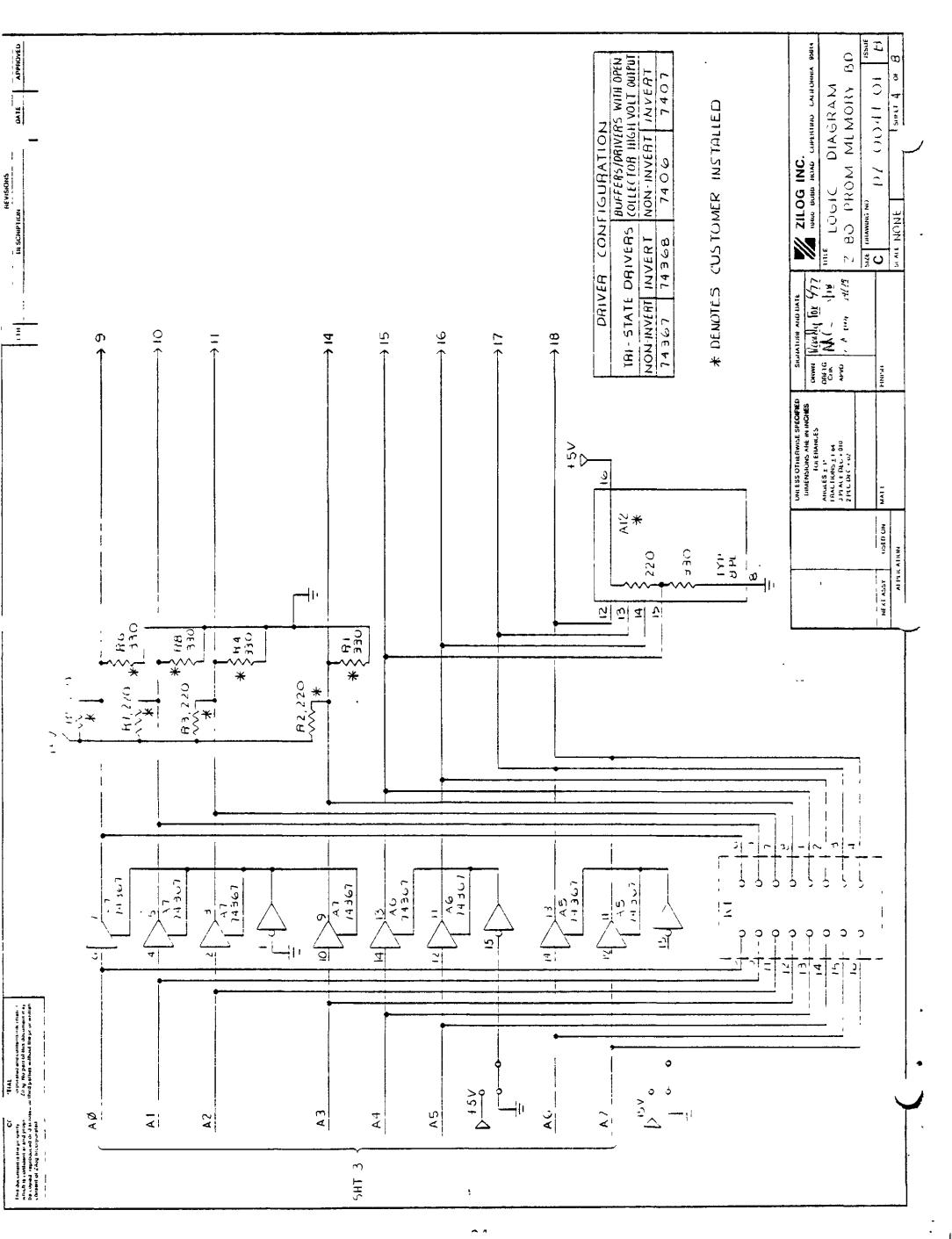

#### Sheet 4

I/O options for PIO channel A are shown on Sheet 4. When port A is in the input mode, jumpers are connected at K1, output buffers are disabled and termination resistors are connected. In the output mode, the jumpers at K1 are removed and the output buffers are enabled. Depending upon the application, several different types of I/O buffers may be used.

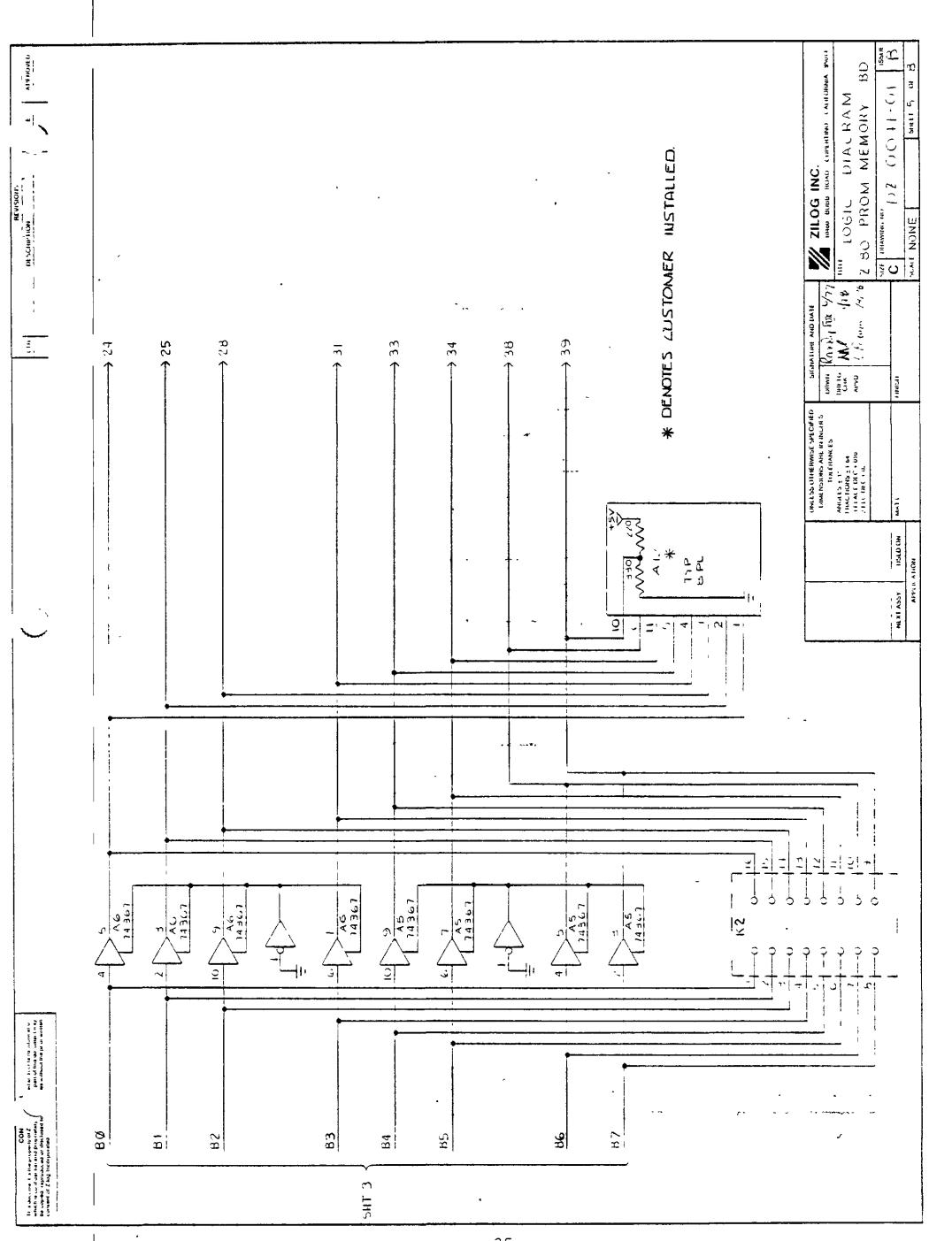

#### Sheet 5

I/O options for PIO channel B are shown on Sheet 5. When port B is in the input mode, jumpers are connected at K2, output buffers are disabled, and termination resistors are connected. In the output mode, the jumpers at K1 are removed and the output buffers are enabled.

#### Sheet 6

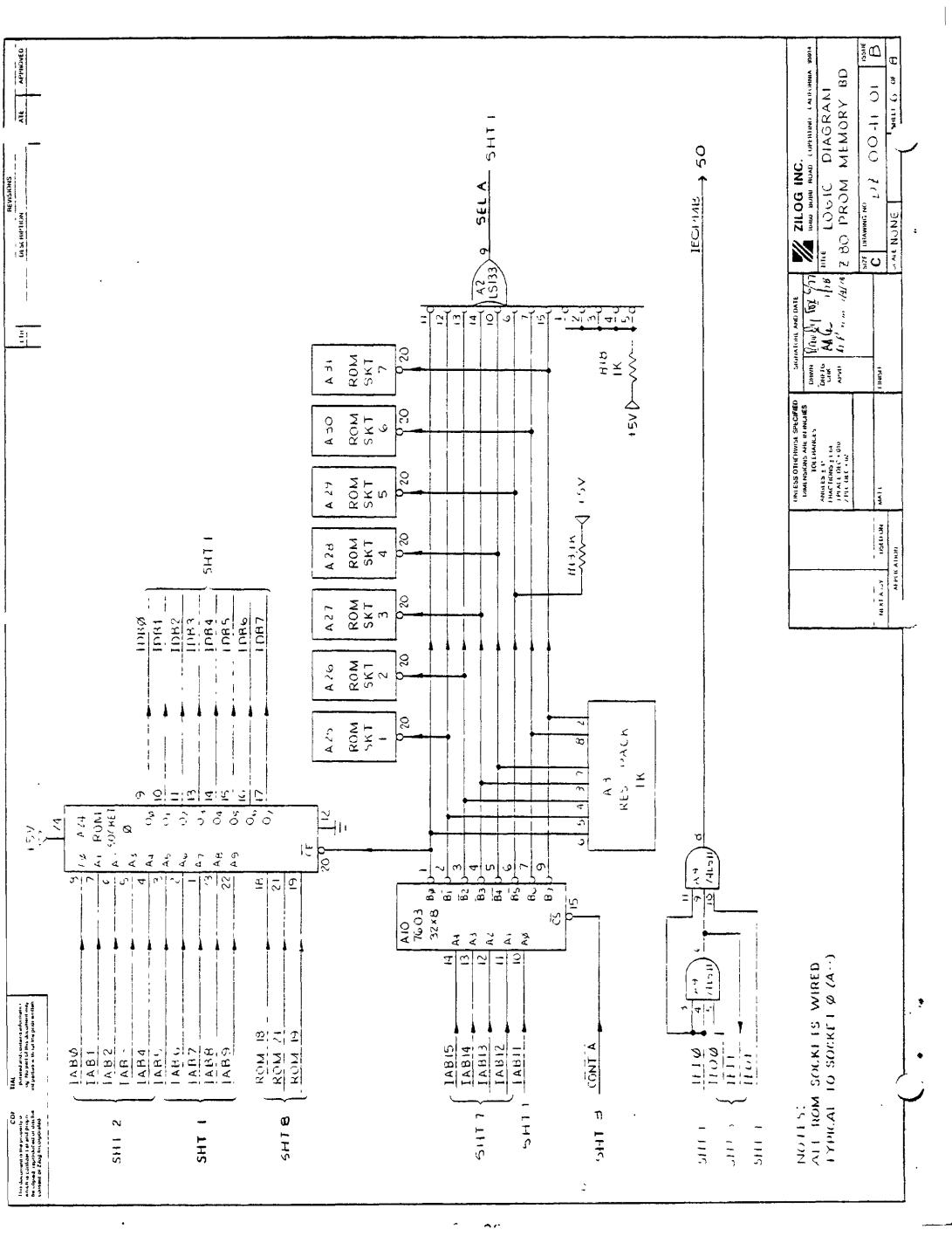

Sheet 6 contains the first bank of eight PROMs and an address decoder PROM. IAB15-IAB11 are input to the decoder PROM and select the location of each of the PROMs on 2K boundaries. Output SEL A indicates to the data bus buffer direction control (Sheet 1) that one of the PROMs in this bank has been selected. Sheet 6 also contains the logic to generate the PMB interrupt enable out.

#### Sheet 7

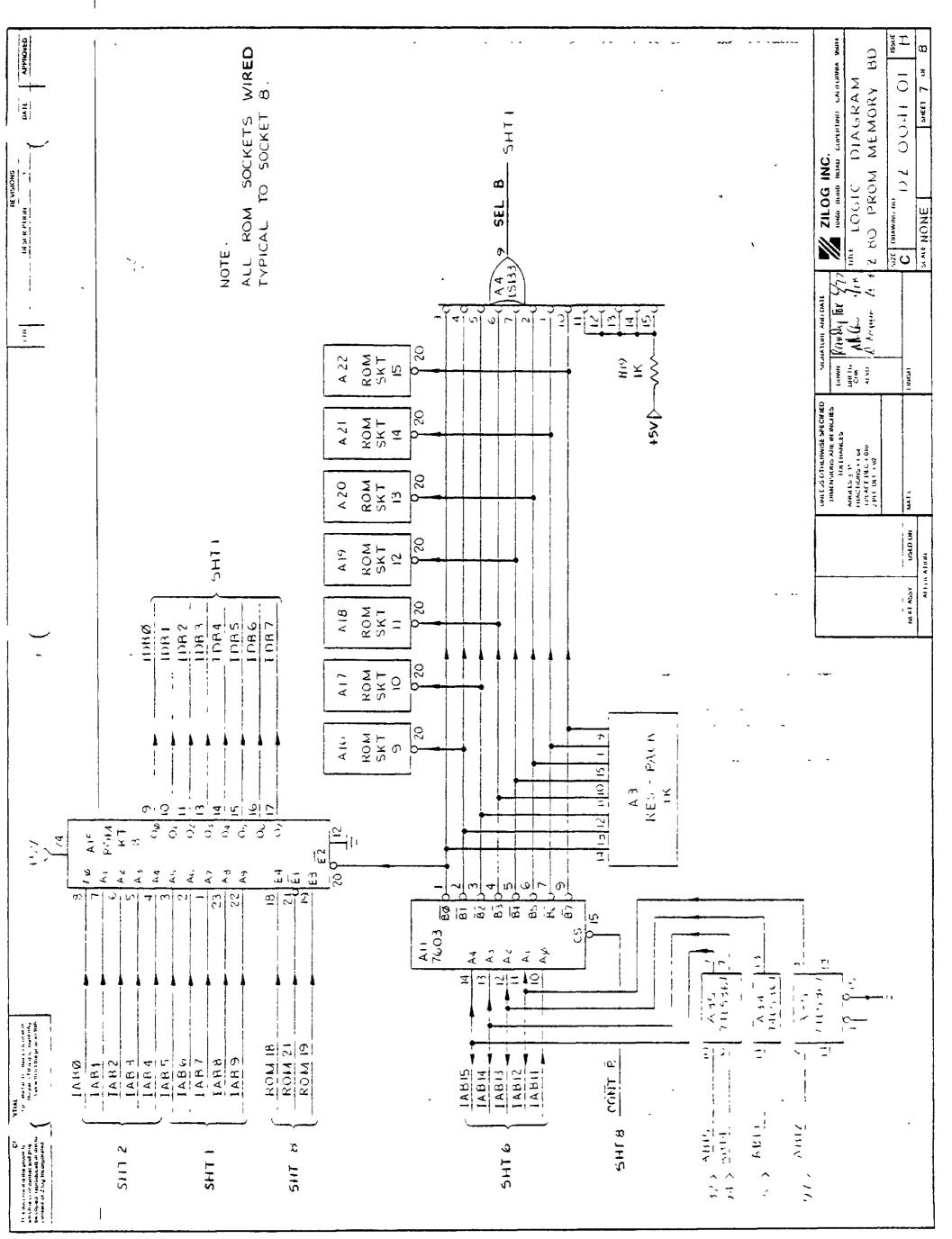

Sheet 7 contains the second bank of eight PROMs and an address decoder PROM. Output SEL B indicates to the data bus buffer direction control (Sheet 1) that one of the PROMs in this bank has been selected. Sheet 7 also contains buffers for the four most significant address bits.

#### Sheet 8

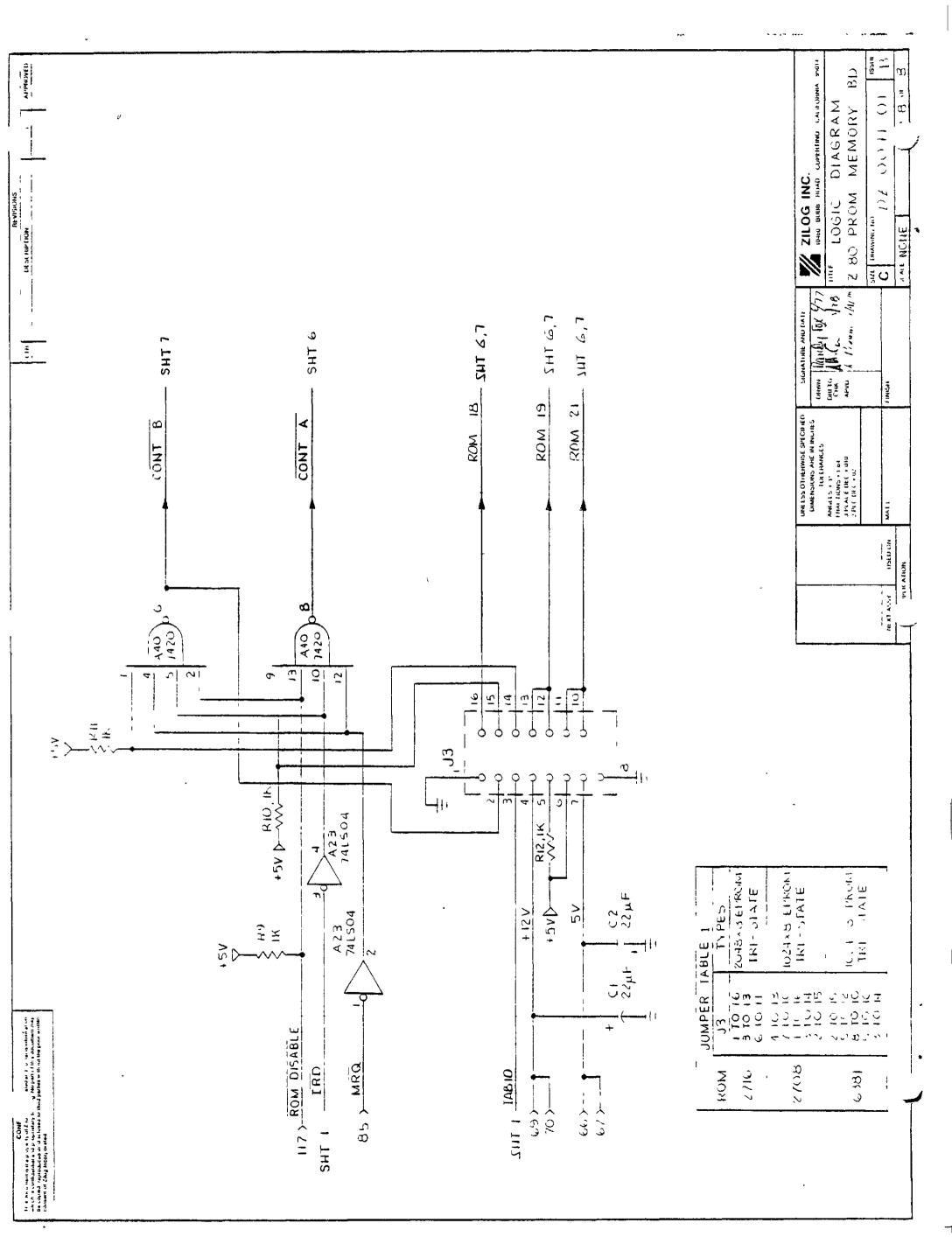

Sheet 8 contains the logic for PROM bank selection, and the jumper area for selecting a particular type of PROM. For PROMs requiring +5V and -12V, backplane connections must be made to the MCZ power supply or other external supplies. See Jumper Table 1 (Sheet 8) for a description of the required jumpers for each type of PROM.

### 6.5 PMB Specification

#### MEMORY SIZE:

Sixteen 24-pin sockets for up to 32 KBYTES of PROM/EPROM

#### MEMORY TYPE:

2708, 2716, 6381

#### INTERFACE:

TTL interface, with MCZ series data, address, and control signals.

#### ADDRESS SELECTION:

PROM programmable for unique addressing of each PROM socket.

#### PARALLEL I/O:

16 programmable bidirectional I/O lines.

#### COUNTER/TIMER:

4 programmable counter/timer channels.

#### **ELECTRICAL SPECIFICATIONS:**

DC POWER

| +12V |         | 0.80A | 1.28A |       |       |       |       |

|------|---------|-------|-------|-------|-------|-------|-------|

| -5V  |         | 0.48A | 0.96A |       |       |       |       |

| +5V  | 0.60A   | 0.70A | 0.84A | 1.59A | 2.28A | 2.84A | 3.40A |

|      |         | TYP   | MAX   | TYP   | MAX   | TYP   | MAX   |

|      | MEMORY  | WITH  | 2708  | WITH  | 2716  | WITH  | 6381  |

|      | WITHOUT | •     |       |       |       |       | *     |

#### CONNECTOR:

122-pin edge (100 mil spacing) available from:

VENDOR

GARRY MFG. CO.

AUGAT

PART NO. 4000-2 14005-19P1

#### PHYSICAL CHARACTERISTICS:

LENGTH: 7.7 in/19.6cm DEPTH: 7.5 in/19.1cm

THICKNESS: .062 in/0.16 cm

SPACING BETWEEN CARDS: 0.5 in/1.27cm centers

MAX COMPONENT HEIGHT: 0.4 in/1.02cm

ETCH LAYERS: TWO

#### **ENVIRONMENT:**

0 to 50 degrees centigrade

#### BURN IN REQUIREMENTS:

Prior to final test, the PMB shall burn in for 96 hours at 45 degrees C, and VCC at 5.3V +/-2%. (5.2V to 5.4V) If any component is replaced after burn in, either component or the entire board must undergo an additional 48 hours at temperature and voltage.

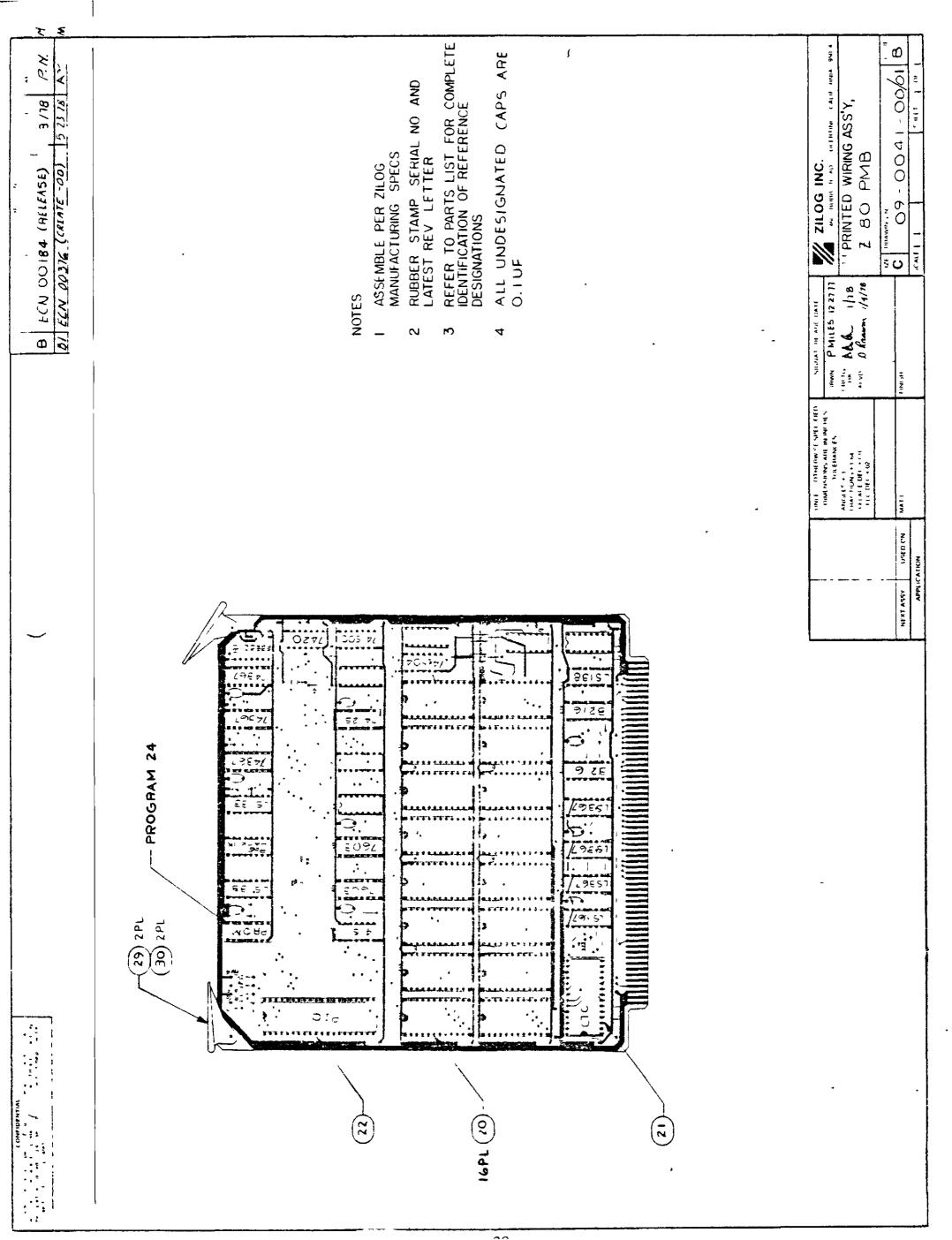

#### 6.6 PMB Parts List

```

1

PCB, BLANK, REV. B

10-0041-01

1

2

Al

I.C., PROM

33-0053-24

1

3

I.C.,74LS133

33-0170-01

2

A2,4

4

I.C.,74367

33-0008-01

3

A5,6,7

5

I.C., PIO

33-0057-01

1

A8

6

I.C.,74LS11

A9

33-0061-01

1

7

I.C.,7603

2

33-0164-00

A10,11

8

I.C.,74125

33-0035-01

1

A13

9

I.C.,74LS00

33-0058-01

1

A14

I.C.,74LS04

33-0059-01

1

A23

10

11

I.C.,CTC

33-0078-01

1

A32

12

I.C.,74LS367

33-0055-01

A33,34,35,36

4

A37,38

13

I.C.,3216

2

33-0089-01

33-0068-01

14

I.C.,74LS138

1

A39

15

I.C.,7420

1

A40

33-0026-01

16

RES.NET.1K

47-0000-01

1

Α3

RES.NET, 220/330

Al2 (NOT SUPPLIED)

17

0

47-0000-02

18

SOCKET, I.C., 14-PIN

21-1000-06

1

A13

19

SOCKET, I.C., 16-PIN

21-1000-02

12

A1,5,6,7,10,11,12,

J1,J2,J3,K1,K2

20

SOCKET, I.C., 24-PIN

21-1000-03

16

A15-22, A24-31

21

SOCKET, I.C., 28-PIN

21-1000-04

1

A32

22

SCCKET, I.C., 40-PIN

21-1000-01

1

8A

23

RES, 1/4W, 5%, 1K

47-1000-63

R9,10,11,12,13,18,19

R2,3,5,7,14,16 (NOT SUPPLIED)

24

RES,1/4W,5%,220

47-1000-47

0

25

RES,1/4W,5%,330

47-1000-51

R1,2,6,8,15,17 (NOT SUPPLIED)

26

15-0003-25

CAP,22UF,15V

4

C1,2,3,4

CAP, 0.1UF, 50V

25

C5-C29

27

15-0000-50

28

1

CRl

DIODE, 1N4001

48-1000-01

EJECTOR, BLANK

2

29

24-0001-01

2

30

91-3000-01

PIN, EJECTOR

31

COMPONENT CARRIER

33-0173-17

1

J1:PIO&CTC PORT SELECT

32

COMPONENT CARRIER

33-0173-18

1

J2:I/O PORT RANGE SELECT

```

## 6.7 Pinout for PROM Memory Board

| PIN #                                                | SIGNAL NAME                                                  |

|------------------------------------------------------|--------------------------------------------------------------|

| 001<br>002<br>003<br>004<br>005                      | +5V<br>+5V<br>+5V<br>IORQ-<br>DB5                            |

| 006<br>007<br>008<br>009<br>010<br>011               | IEI.PMB.PIODB3 PIO.O.AOPIO.O.A1 PIO.O.A2                     |

| 012<br>013<br>014<br>015<br>016<br>017               | DB6 DB0 PIO.O.A3 PIO.O.A4 PIO.O.A5 PIO.O.A6                  |

| 018<br>019<br>020<br>021<br>022<br>023               | PIC.0.A7 PIO.0.A.RDY PIO.0.A.STRB- PIO.0.B.RDY PIC.0.B.STRB- |

| 024<br>025<br>026                                    | PIO.O.BO<br>PIO.O.B1<br>AB7                                  |

| 027<br>028<br>029<br>030                             | AB8<br>PIO.O.B2<br>AB5<br>AB6                                |

| 031<br>032<br>033<br>034                             | PIO.0.B3<br>AB15<br>PIO.0.B4<br>PIO.0.B5                     |

| 035<br>036<br>037<br>038<br>039<br>040<br>041<br>042 | . AB13 AB11 PIO.0.B6 PIO.0.B7 .                              |

| U 1 2                                                | •                                                            |

```

PIN #

SIGNAL NAME

043

044

045

046

047

048

049

IEO.PMB.PIO

050

051

052

053

054

055

056

057

058

IEO.PMB.CTC

059

+5V

060

+5V

061

+5V

062

GND

063

GND

064

GND

065

066

-5V

067

-5V

068

DB4

069

+12V

070

+12V

071

DB2

072

DB7

073

074

075

DBl

076

077

078

079

INT-

080

081

082

083

0\,8\,4

085

MRQ-

086

087

088

089

090

AB9

```

```

PIN ÷

SIGNAL NAME

091

AB10

092

093

094

AB14

095

096

097

AB12

098

AB4

099

PHI-.(SYSTEM CLOCK-)

100

AB3

101

AB2

102

AB1

103

AB0

104

105

106

107

108

109

110

CK/T0

111

CK/Tl

112

CK/T2

113

CK/T3

114

ZC/TC0

115

M1-

116

RD-

117

ROM.DISABLE-.(IN)

118

ZC/TO2

119

ZC/TC1

120

GND

121

GND

122

GND

```

# Zilog

10340 Bubb Road Cupertino, California 95014 Telephone: (408) 446-4666 TWX: 910-338-7621

Oberseering 31

Postfach 60 17 05

2000 Hamburg 60

Telefon 040 / 630 50 67

Telex 02 13 288