ZDS 1/25 HARDWARE USER MANUAL

**PRELIMINARY**

03-3003-02, Revision 1

31 October 1978

Copyright 1978 by Zilog, Inc. All rights reserved. No part of this publication may be reproduced, stored in any retrieval system, or transmitted, in any form or by any means, electronic, mechanical, photocopying, recording or otherwise, without the prior written permission of Zilog.

Zilog assumes no responsibility for the use of any circuitry other than circuitry embodied in a Zilog product. No other circuit patent licenses are implied.

ZDS 1/25 HARDWARE USER MANUAL

PRELIMINARY

. • • 1 ÷

# TABLE OF CONTENTS

| SECTION |                                                      | PAGE                                                                        |

|---------|------------------------------------------------------|-----------------------------------------------------------------------------|

| 1.0     | INTRODUCTION                                         | . 1-1                                                                       |

|         | 1.1 General Information                              | . 1-1<br>. 1-2                                                              |

| 2.0     | INSTALLATION                                         | . 2-1                                                                       |

|         | <pre>2.1 Unpacking</pre>                             | · 2-1<br>· 2-4                                                              |

| 3.0     | MAJOR UNITS                                          | . 3-1                                                                       |

|         | 3.1 General Information                              | . 3-1<br>. 3-1<br>. 3-2                                                     |

|         | (FDC)                                                | . 3-2<br>. 3-2<br>. 3-2<br>. 3-3<br>. 3-4                                   |

| 4.0     | PRINCIPLES OF OPERATION                              | . 4-1                                                                       |

|         | 4.1 General Information                              | <ul> <li>4-1</li> <li>4-1</li> <li>4-1</li> <li>4-2</li> <li>4-3</li> </ul> |

|         | 4.2.6 Address Buffer and Decoder (Sheets 1, 2 and 4) | . 4-4<br>. 4-4<br>. 4-7<br>. 4-13<br>. 4-14<br>. 4-18                       |

| 4.3    | <b>→</b>                              | 4-32 |

|--------|---------------------------------------|------|

| 4.3.1  | Control Logic (Sheet 1)               | 4-32 |

| 4.3.2  | Data Buffers (Sheet 2)                | 4-32 |

| 4.3.3  | Row Address Select (Sheet 1)          | 4-33 |

| 4.3.4  | Address Multiplex (Sheet 2)           | 4-33 |

| 4.3.5  | Dynamic Memory Array (Sheet 4)        | 4-33 |

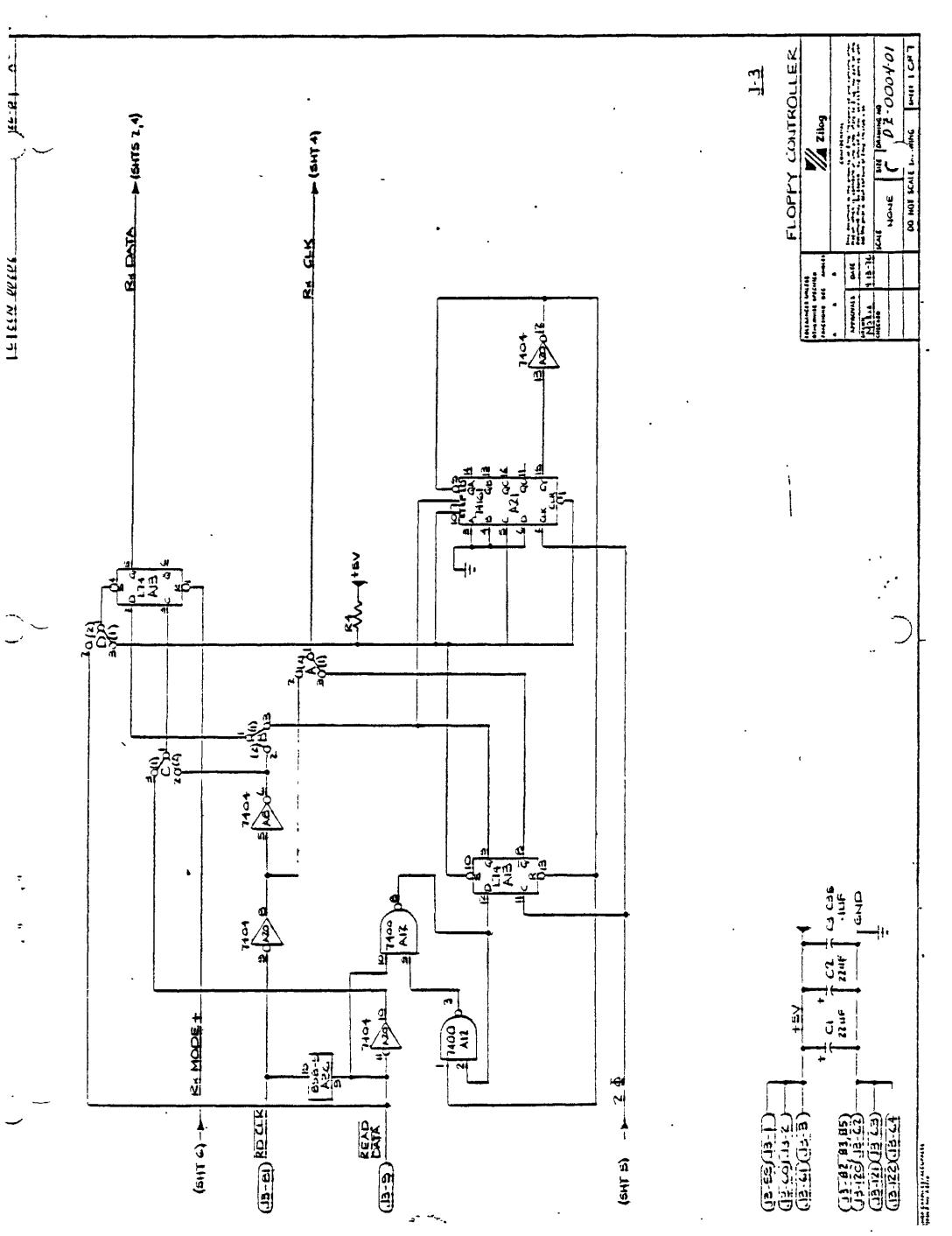

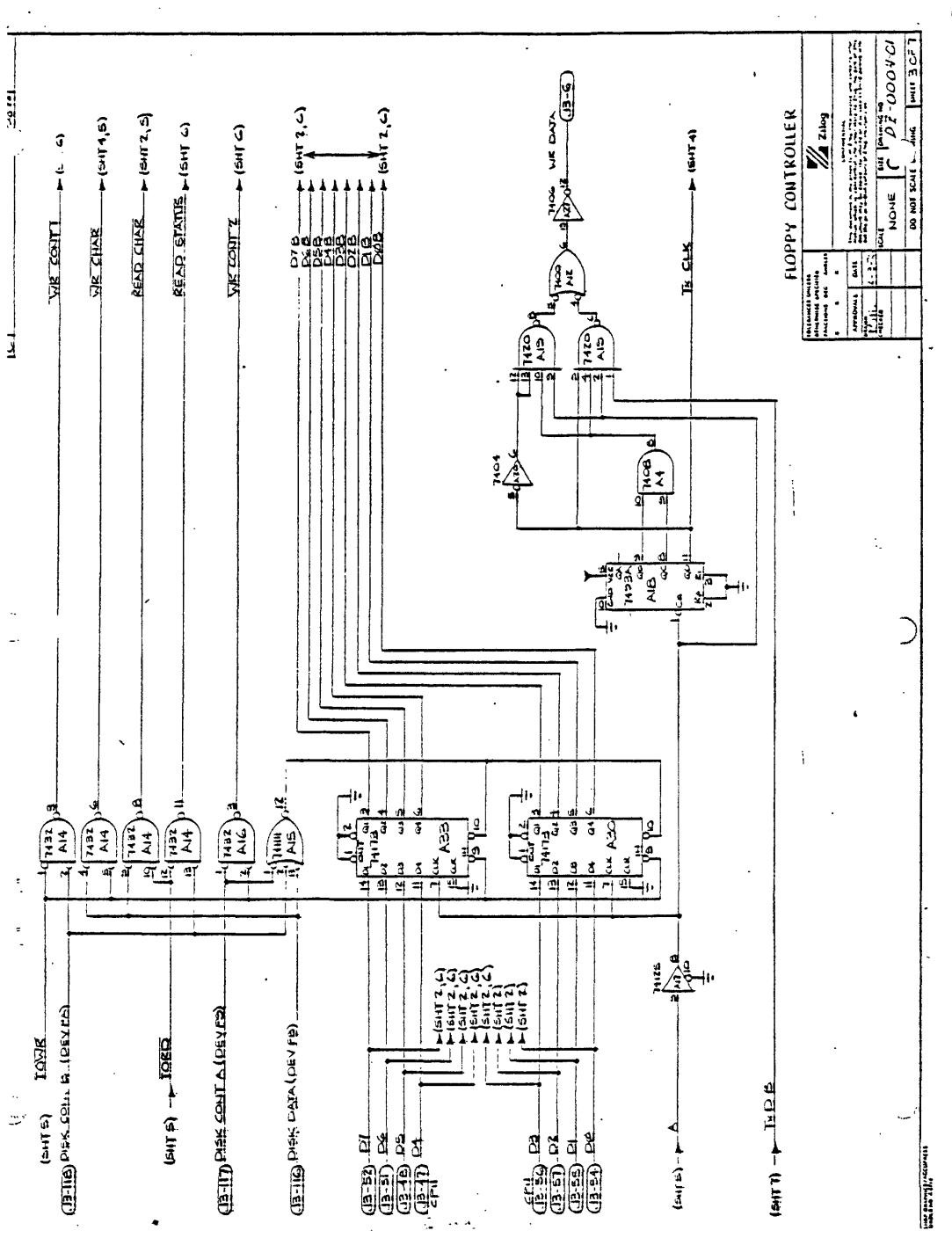

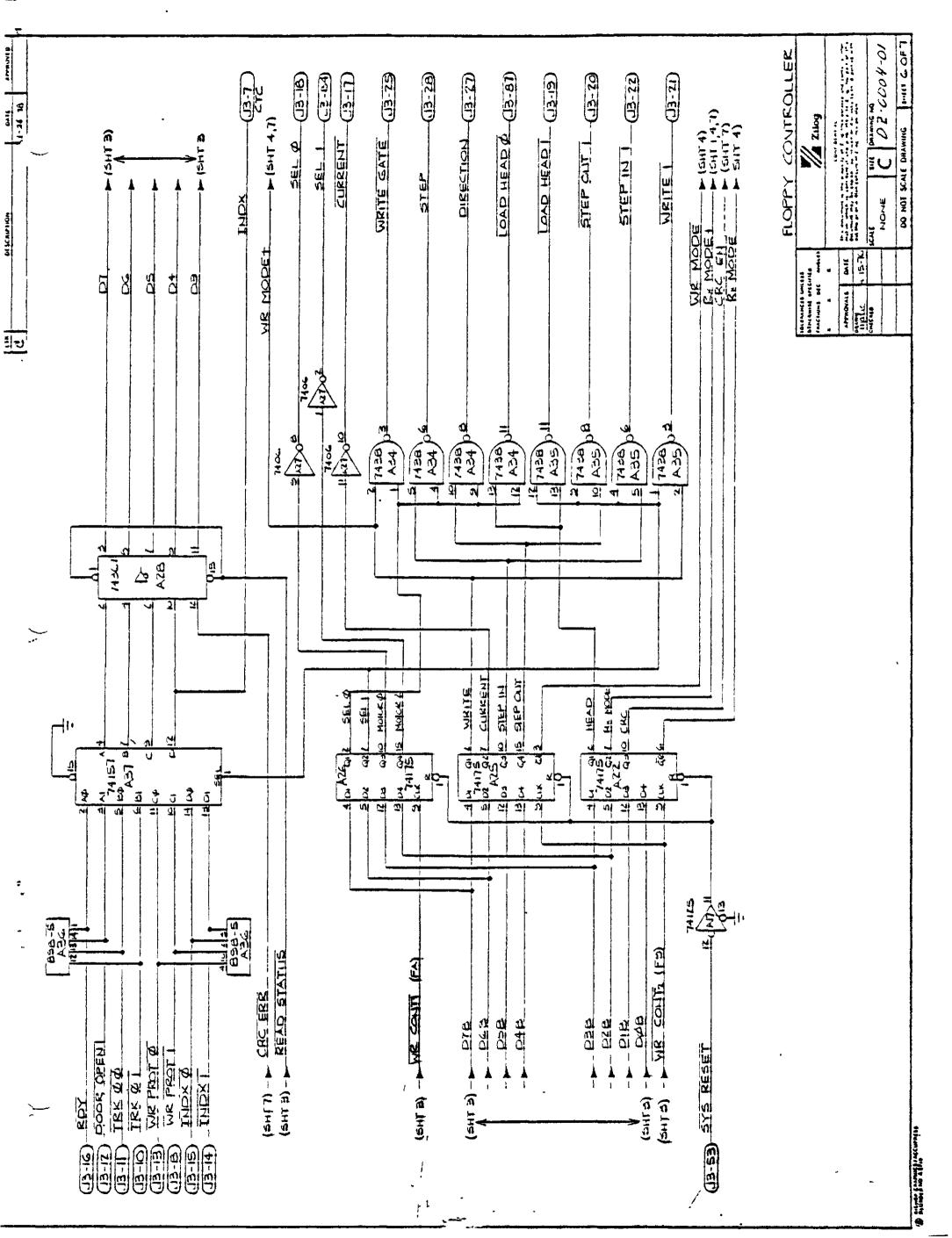

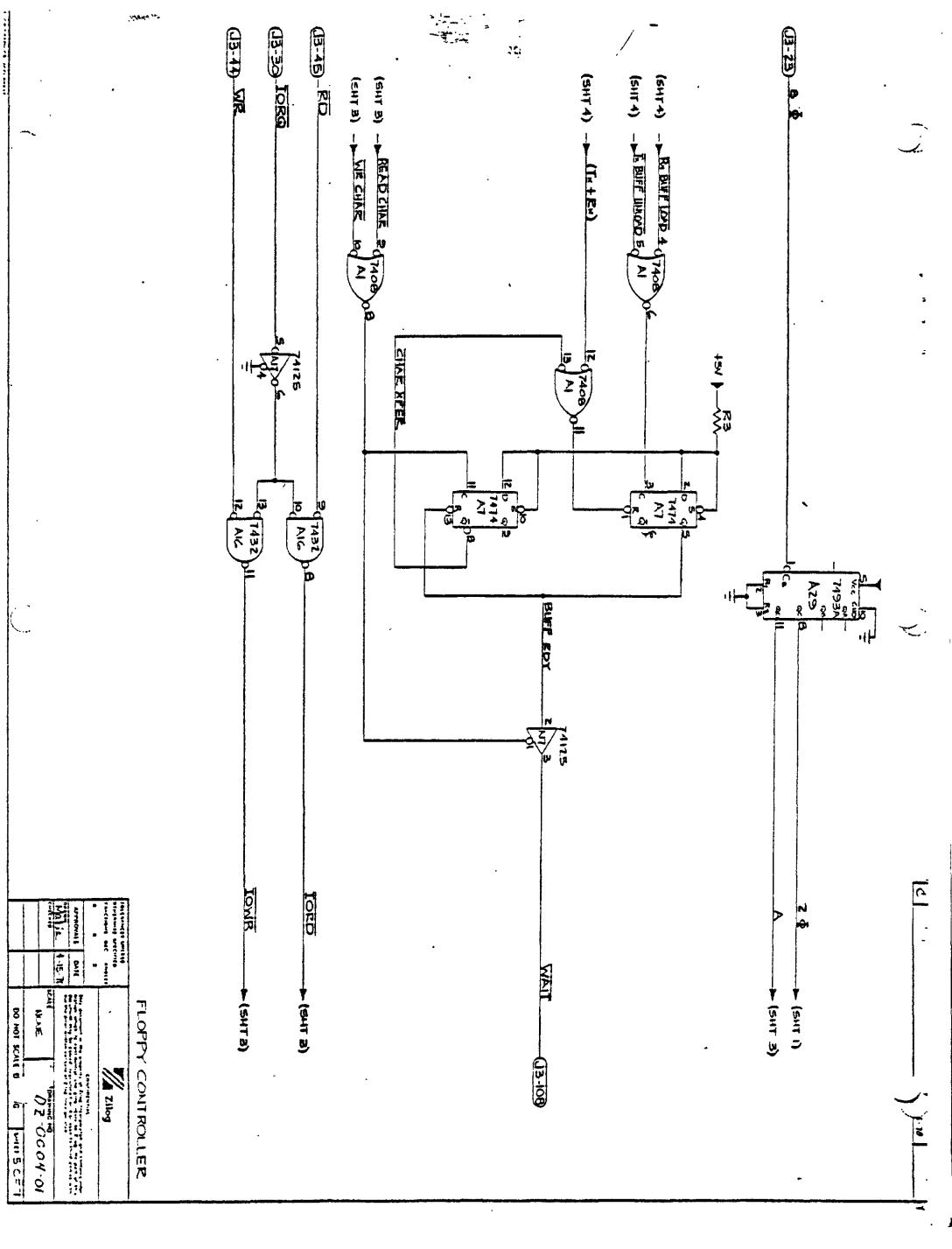

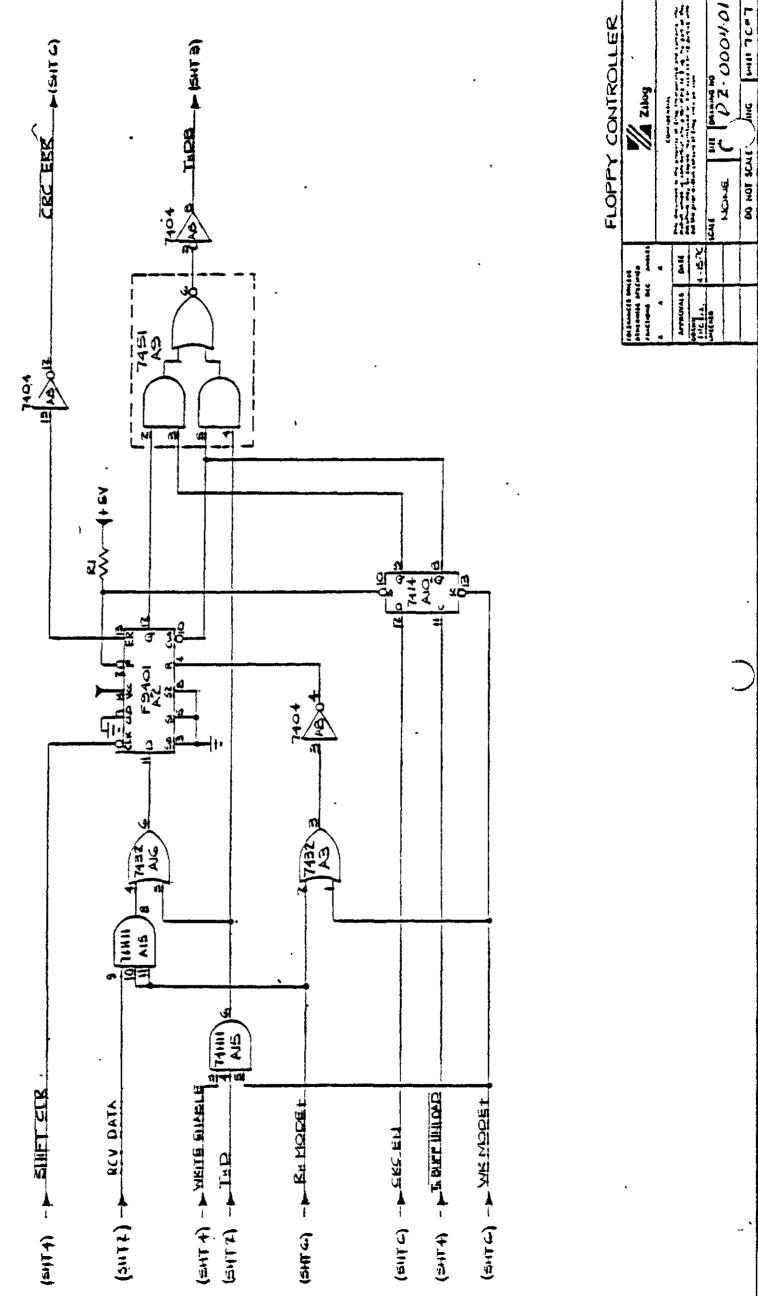

| 4.4    | Floppy Disc Controller Module         | 4-33 |

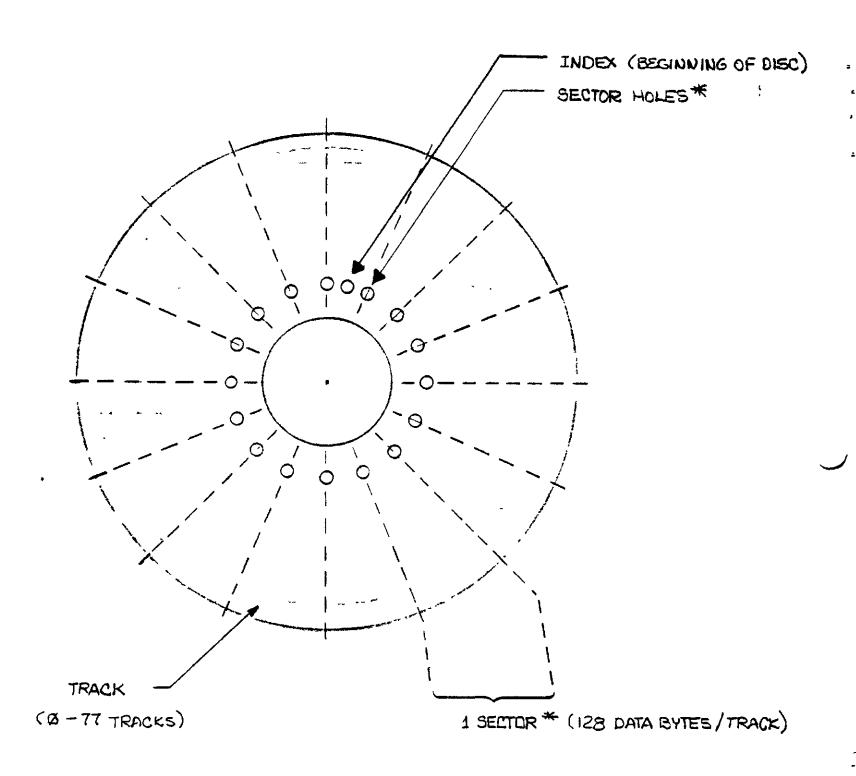

| 4.4.1  | Diskette Format                       | 4-35 |

| 4.4.2  |                                       | 4-35 |

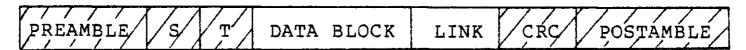

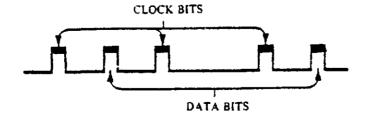

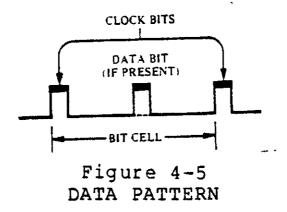

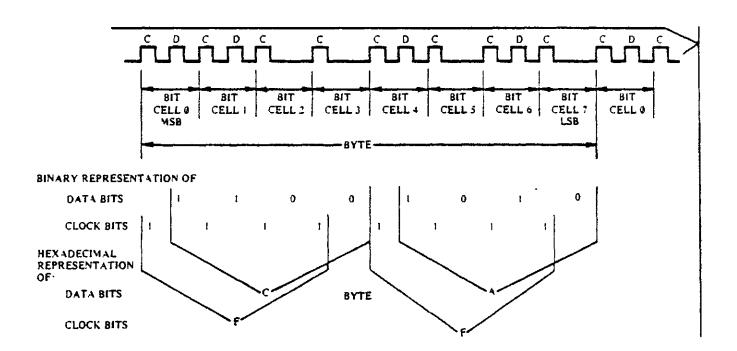

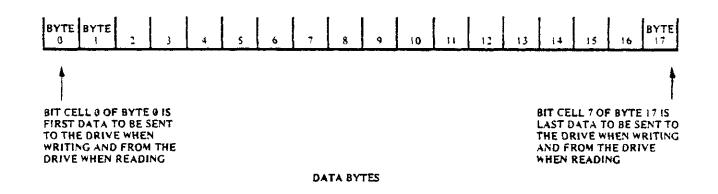

|        | Recording Format                      | 4-36 |

| 4.4.4  | T                                     |      |

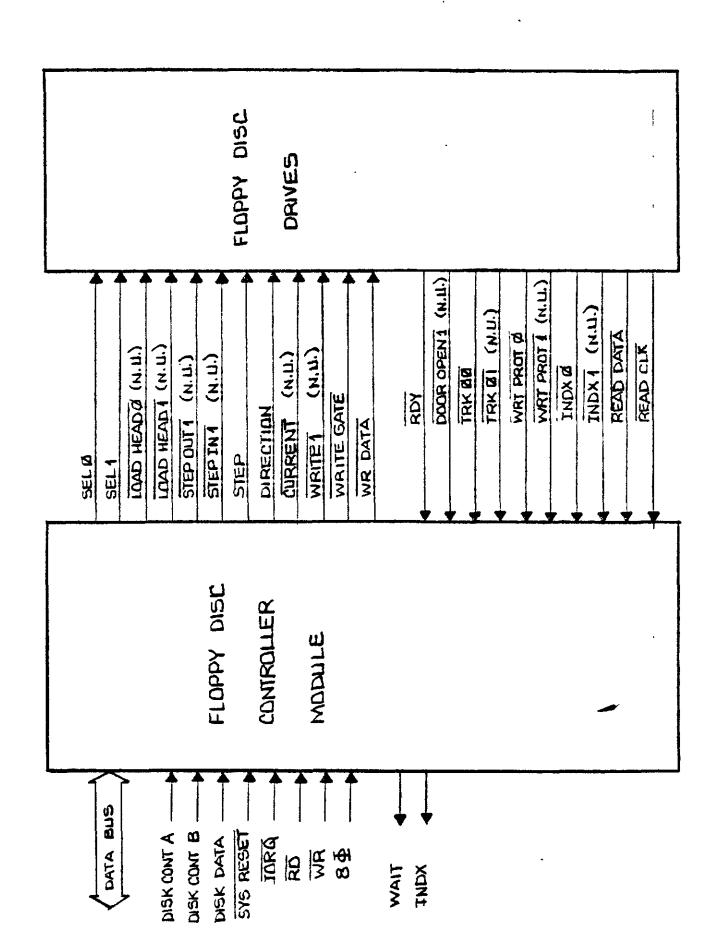

|        | faces                                 | 4-38 |

| 4.4.5  | Floppy Controller - Detailed          |      |

|        | Operation                             | 4-42 |

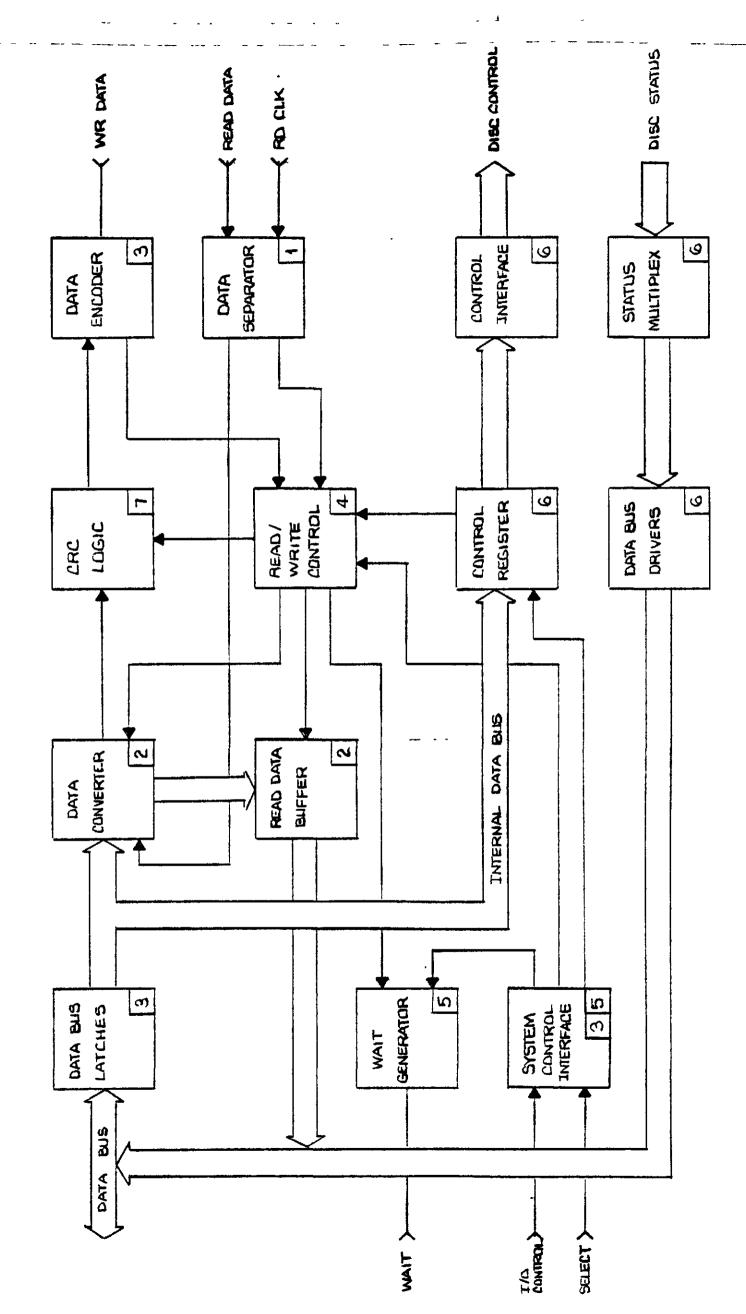

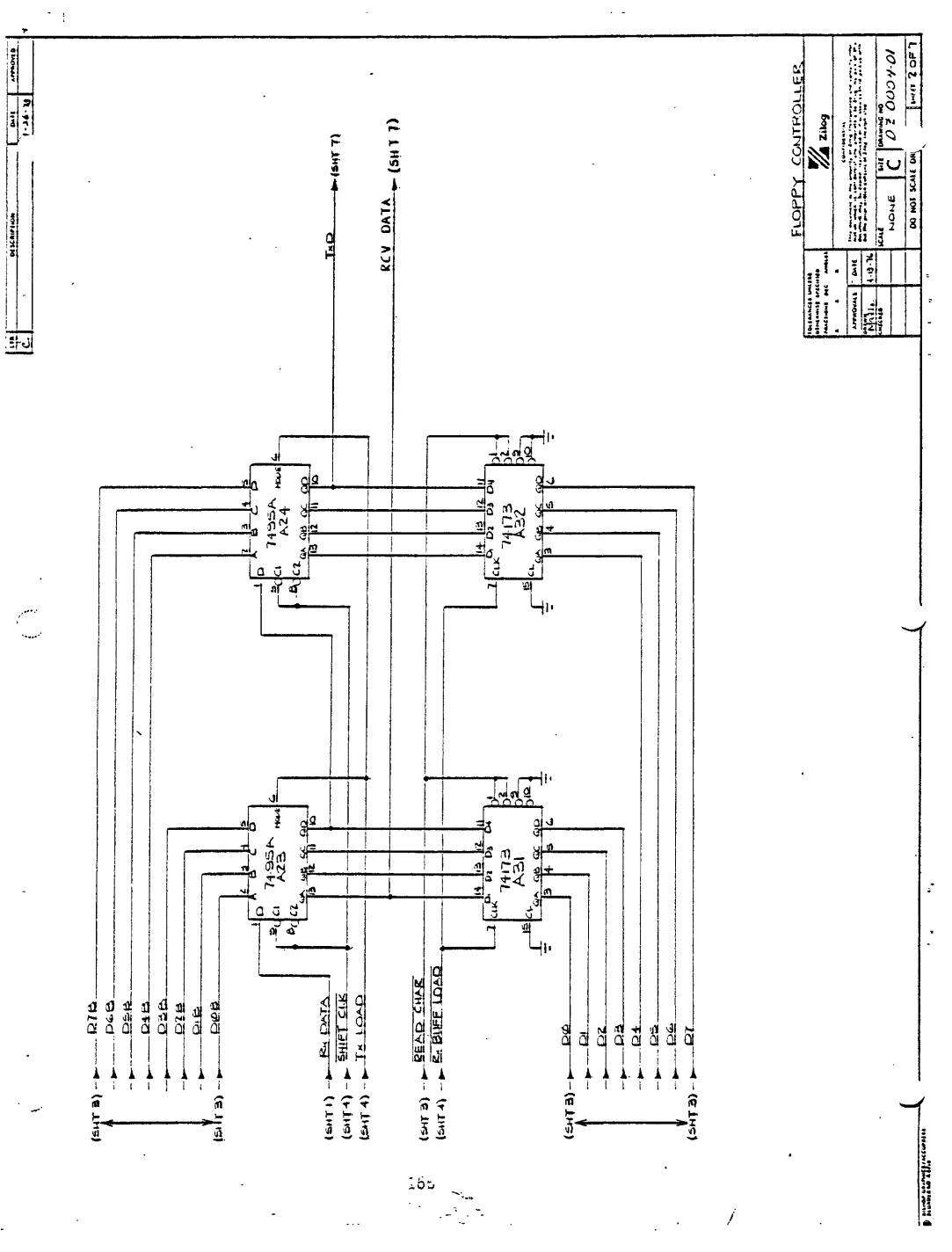

| 4.4.5. | .1 Data Bus Latches (Sheet 3)         | 4-44 |

|        | .2 Data Converter (Sheet 2)           | 4-44 |

|        | .3 Read Data Buffer (Sheet 2)         | 4-44 |

|        | .4 CRC Logic (Sheet 7)                | 4-45 |

|        | .5 Data Encoder (Sheet 3)             | 4-46 |

|        | .6 Data Separator (Sheet 1)           | 4-46 |

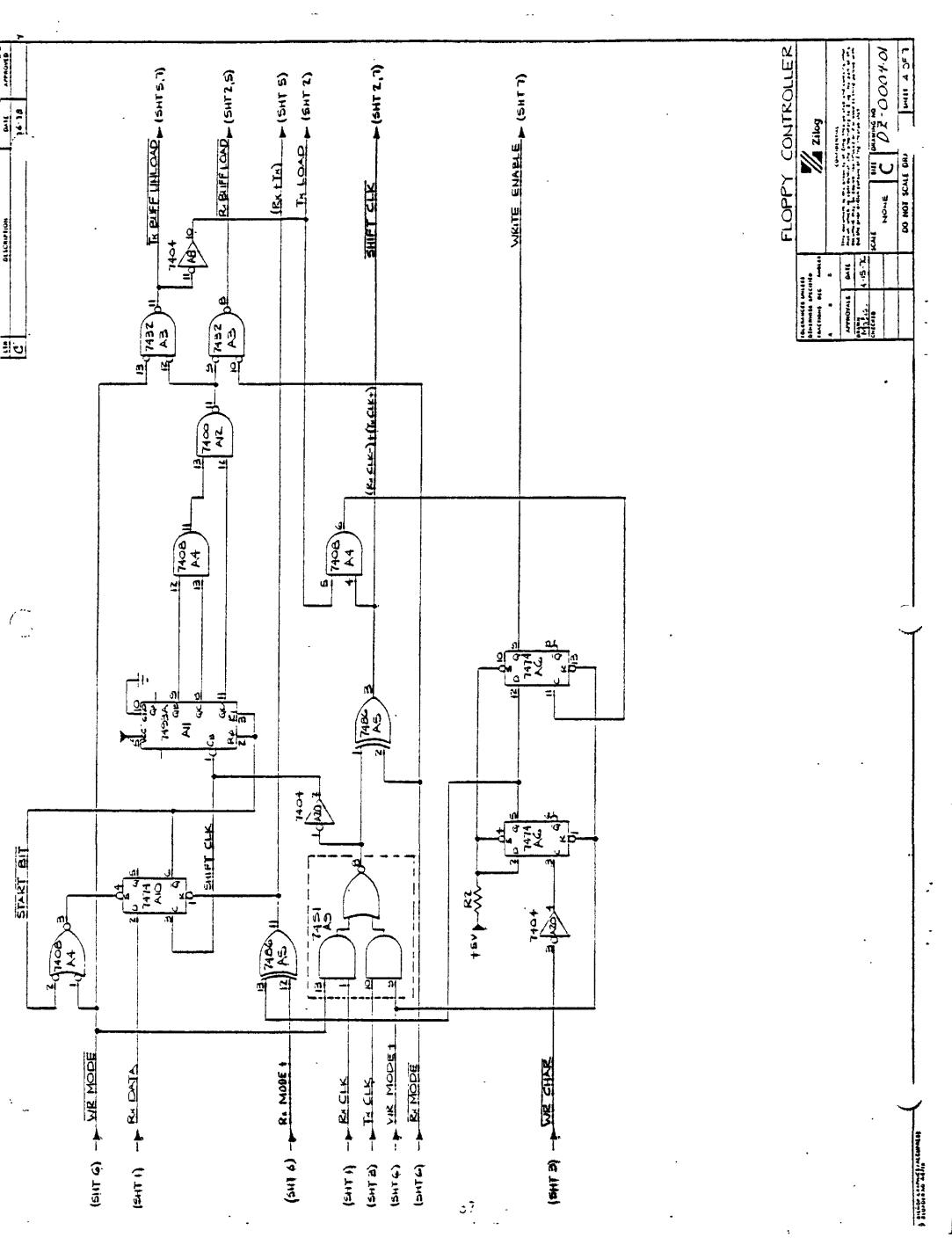

|        | .7 Read/Write Control (Sheet 4)       | 4-46 |

|        | · · · · · · · · · · · · · · · · · · · | 4-40 |

| 4.4.0  | .8 System Control Interface           | 4-47 |

| 4 4 5  | (Sheet 3)                             | 4-47 |

|        | .9 Wait Generator (Sheet 5)           |      |

|        | .10 Control Register (Sheet 6)        | 4-48 |

|        | .11 Control Interface (Sheet 6)       | 4-48 |

|        | .12 Status Multiplex (Sheet 2)        | 4-48 |

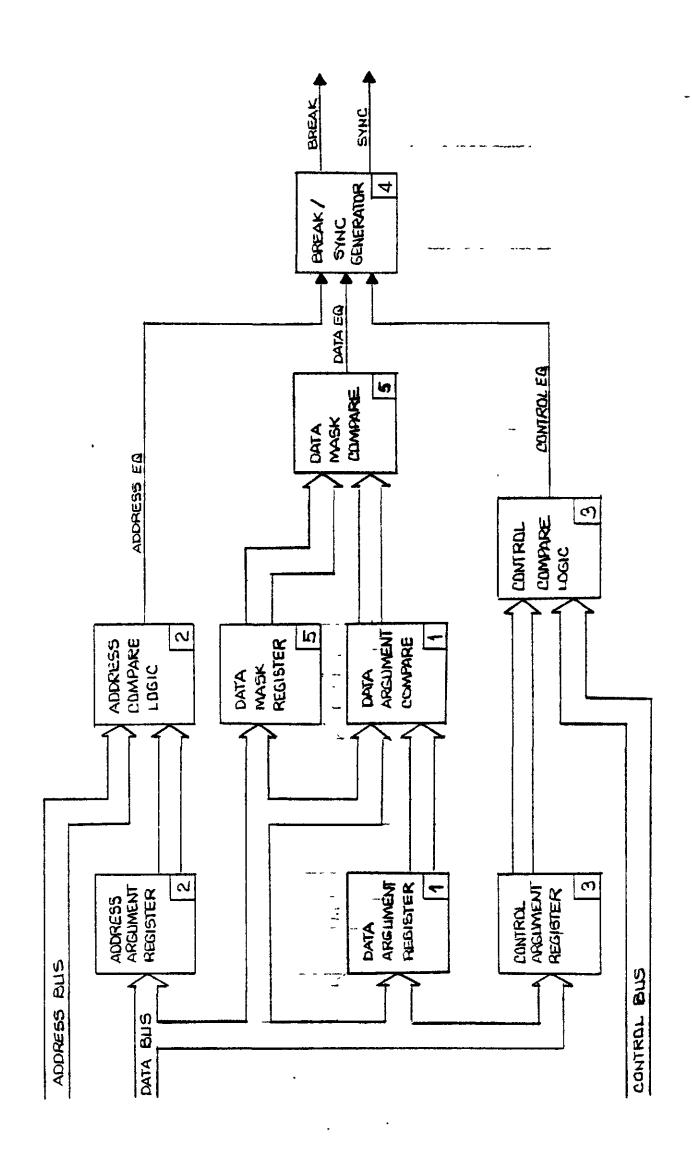

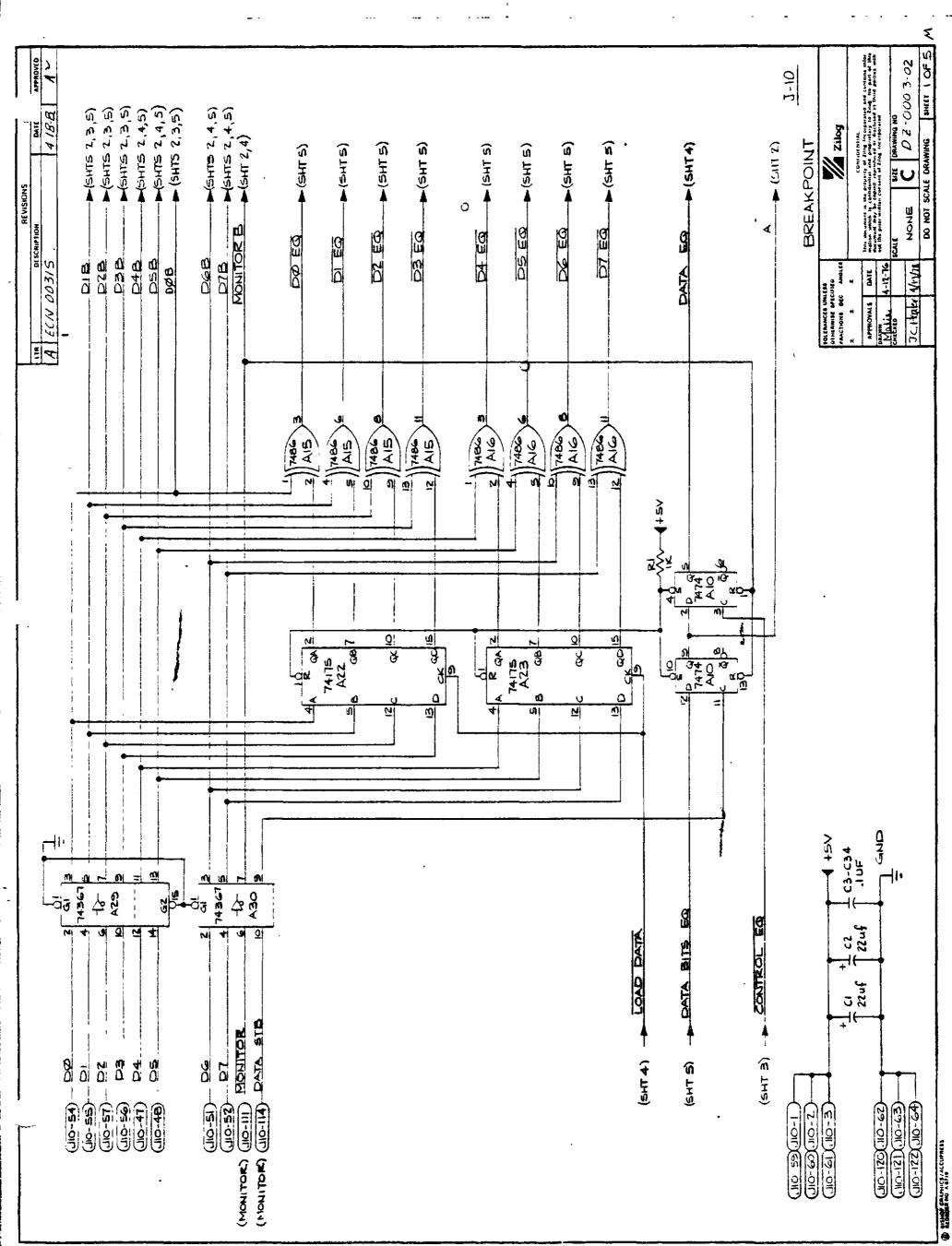

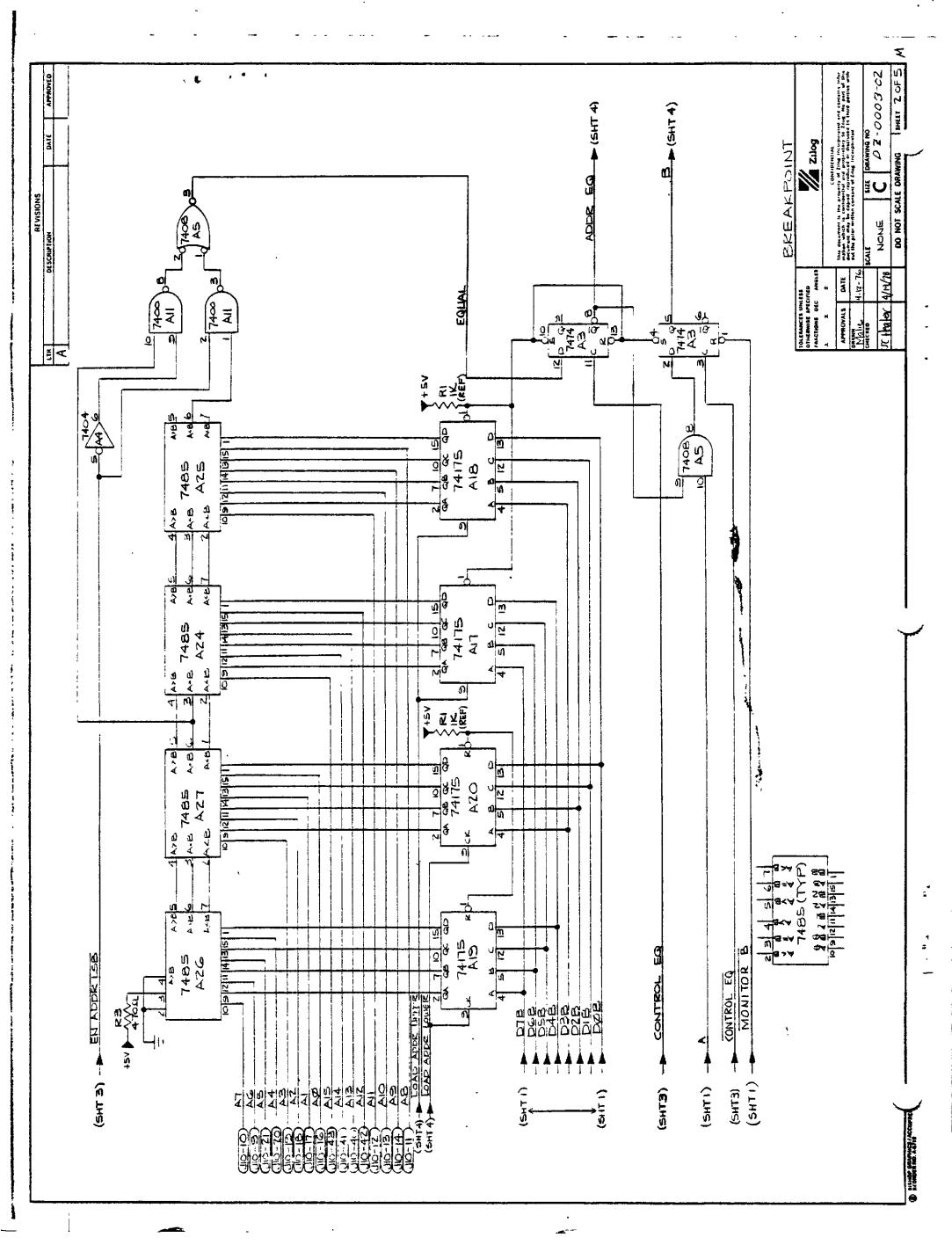

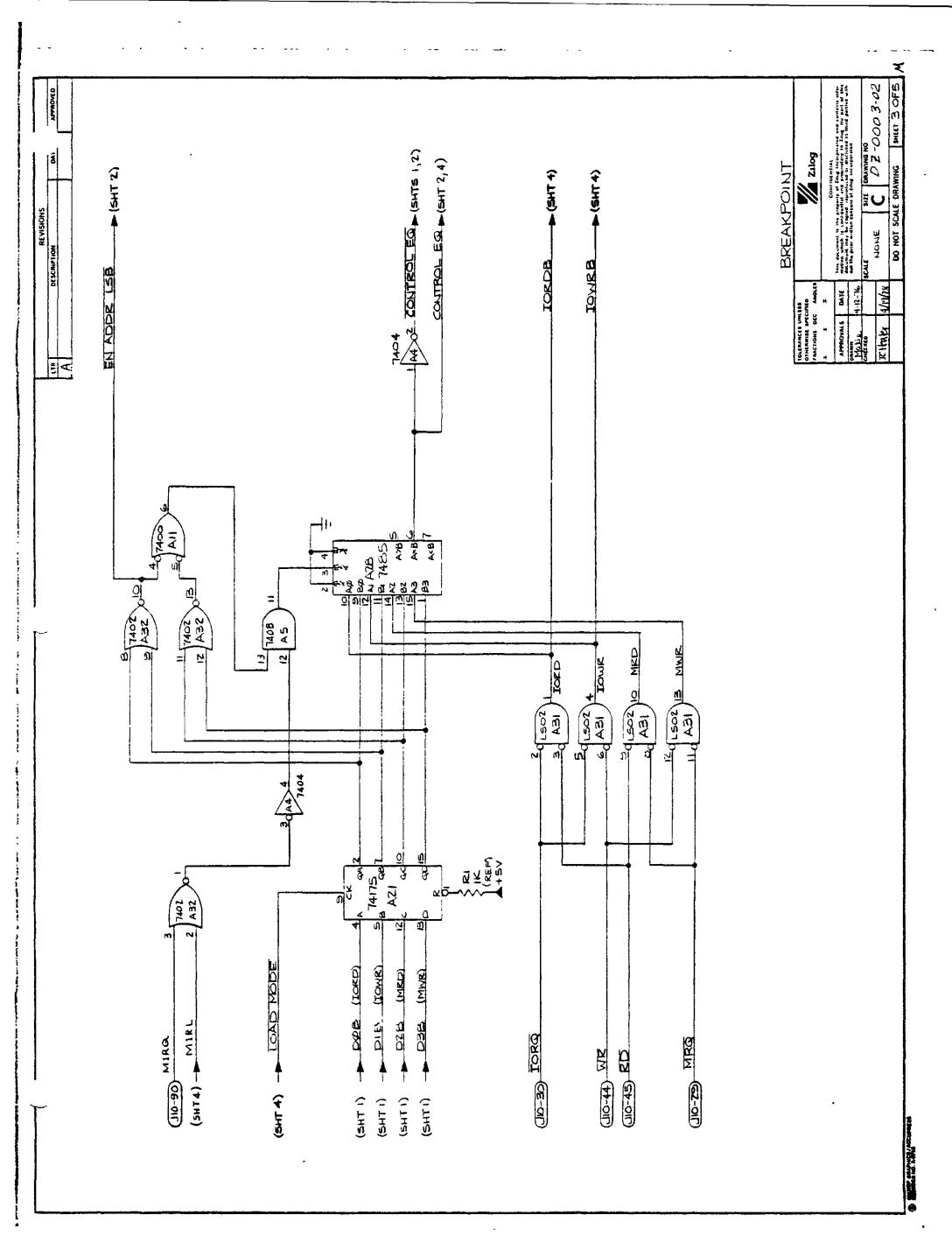

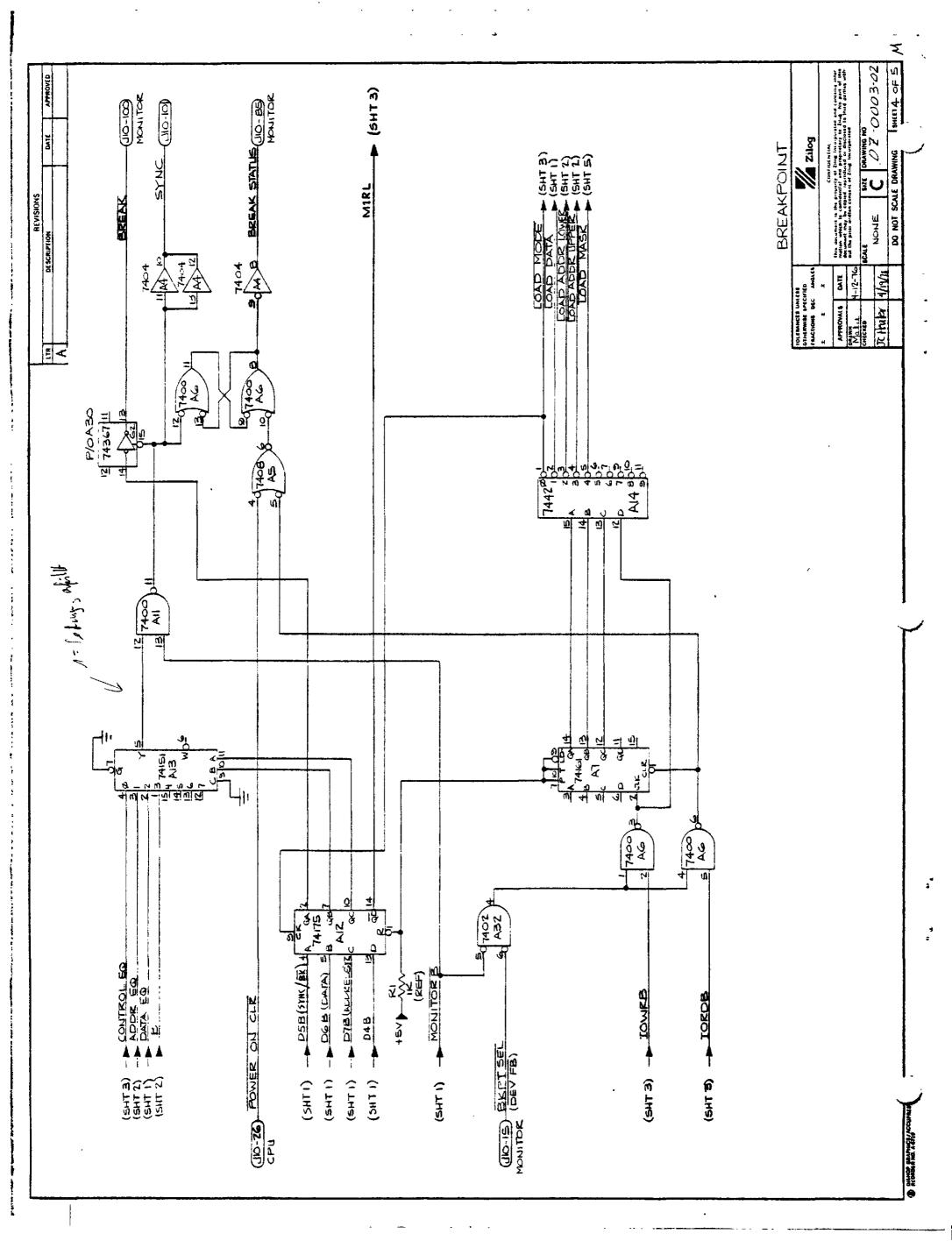

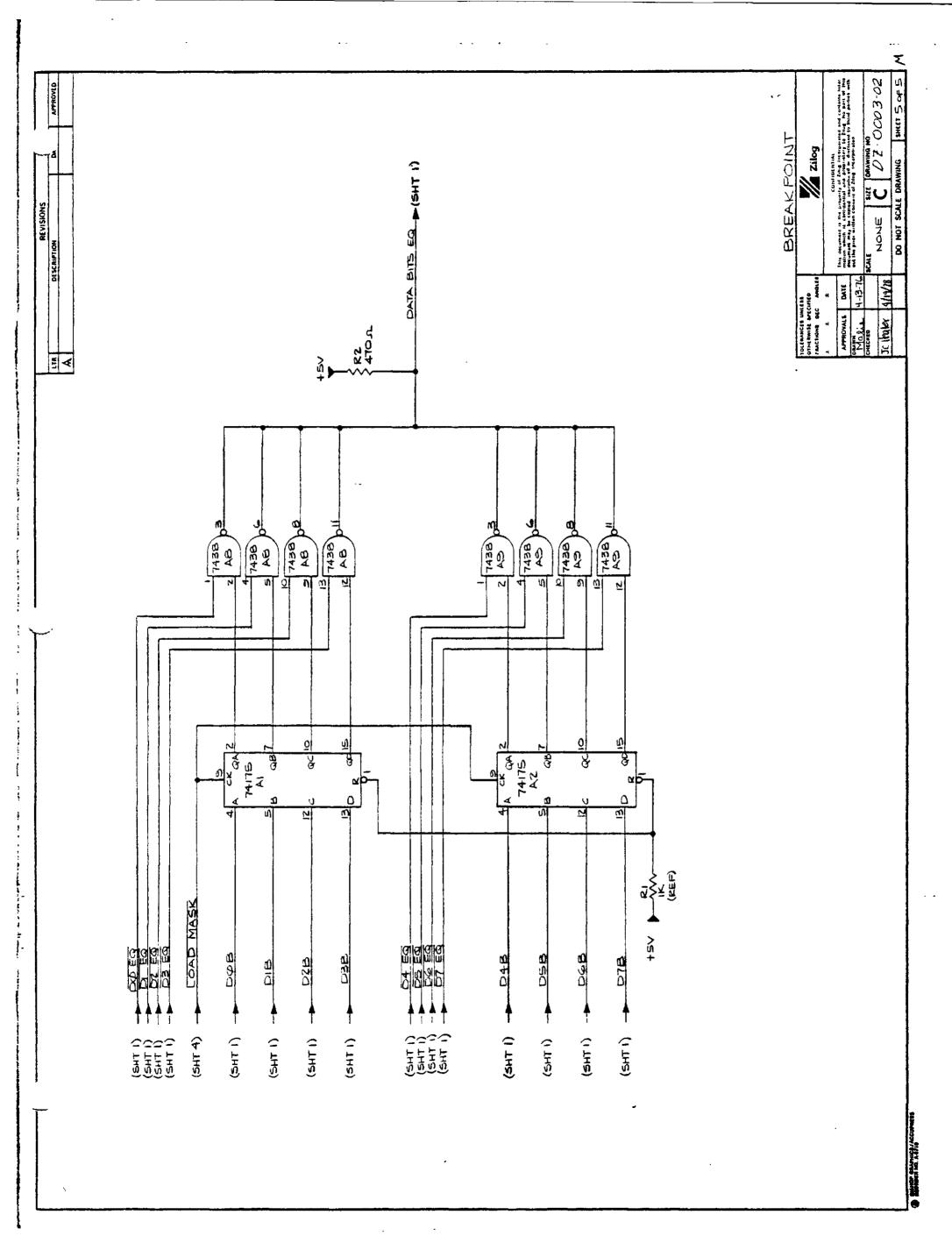

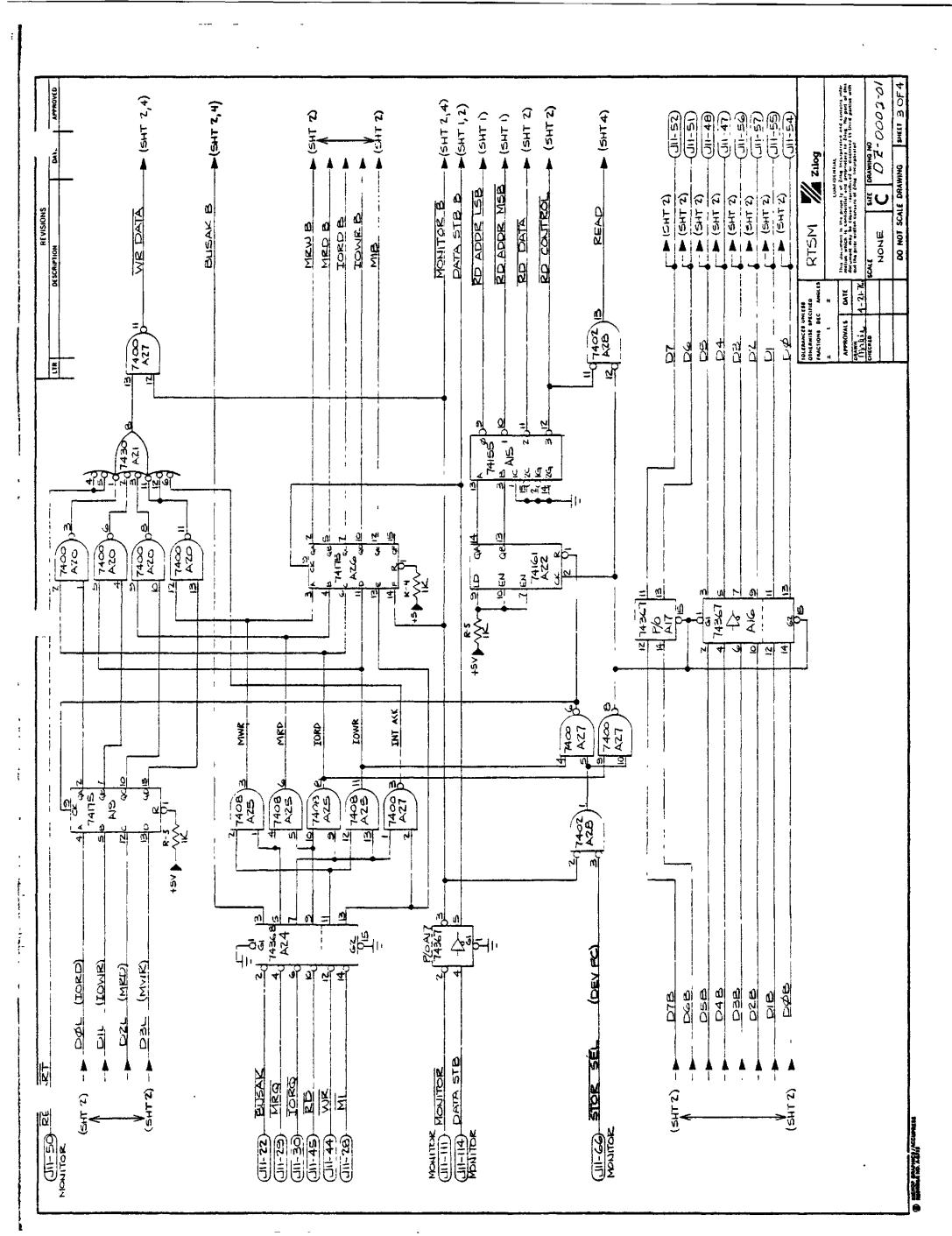

|        | Breakpoint Module                     | 4-50 |

|        | Control Logic                         | 4-50 |

| 4.5.2  | Address Argument Register             | 4 53 |

|        | (Sheet 2)                             | 4-53 |

|        | Address Comparators (Sheet 2)         | 4-53 |

|        | Data Argument Register (Sheet 1)      | 4-53 |

| 4.5.5  | Data Argument Compare Logic           |      |

|        | (Sheet 1)                             | 4-53 |

|        | Data Mask Register (Sheet 5)          | 4-54 |

| 4.5.7  | Data Mask Compare Logic               |      |

|        | (Sheet 5)                             | 4-54 |

| 4.5.8  | Control Argument Register             |      |

|        | (Sheet 3)                             | 4-55 |

|        | Control Compare Logic (Sheet 3)       | 4-55 |

| 4.5.10 | O Break/Sync Generator (Sheet 4)      | 4-55 |

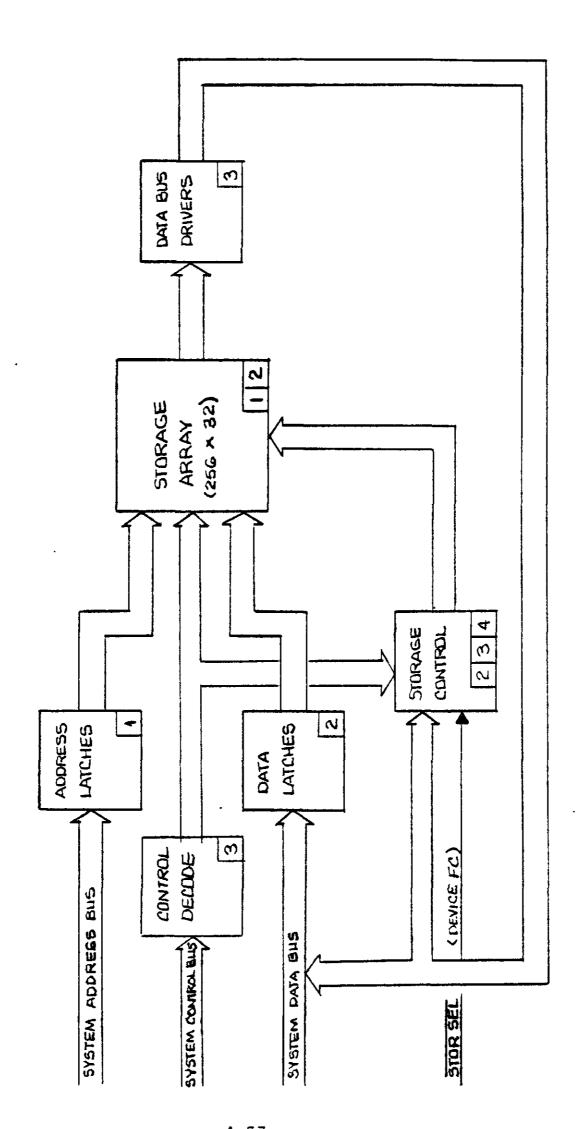

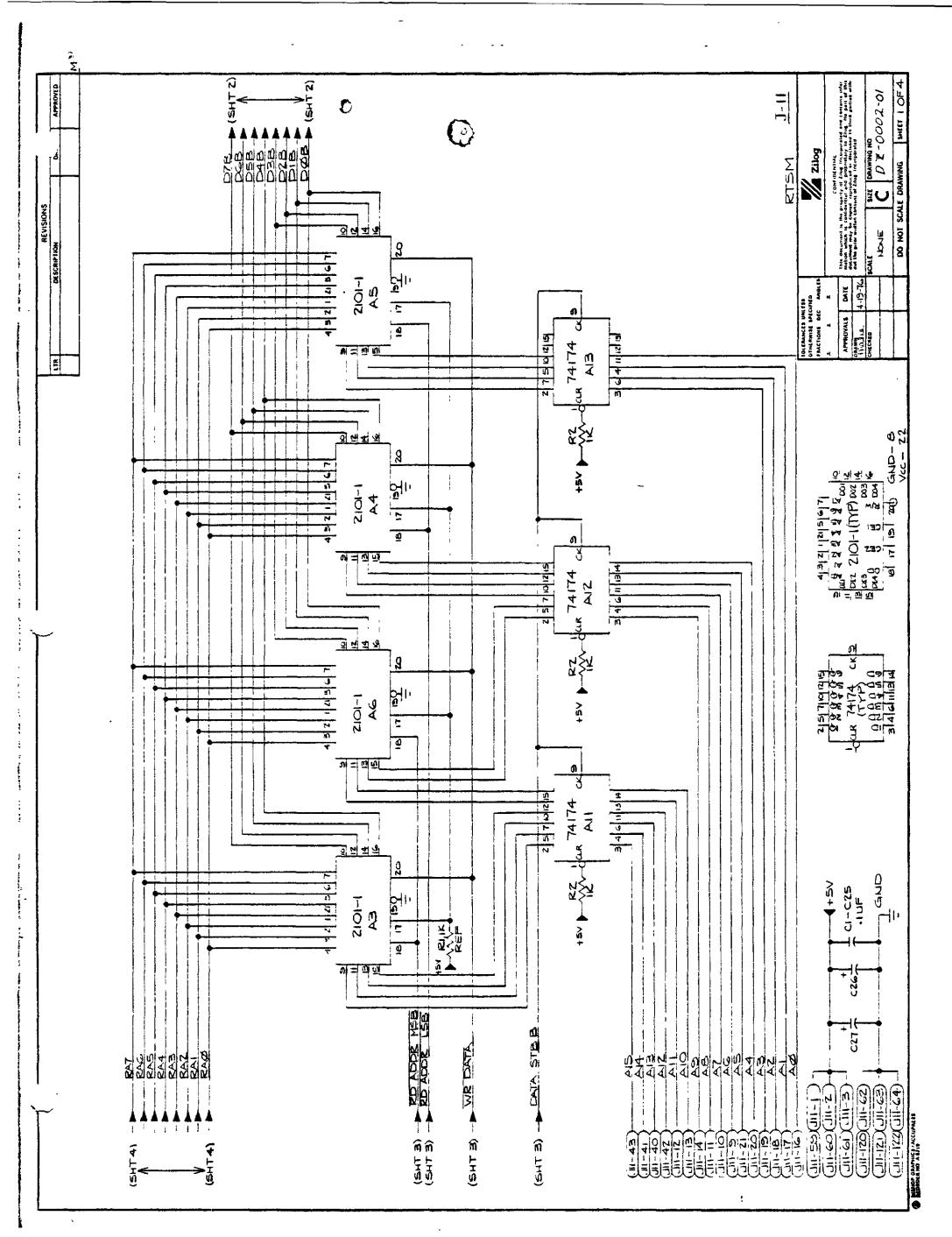

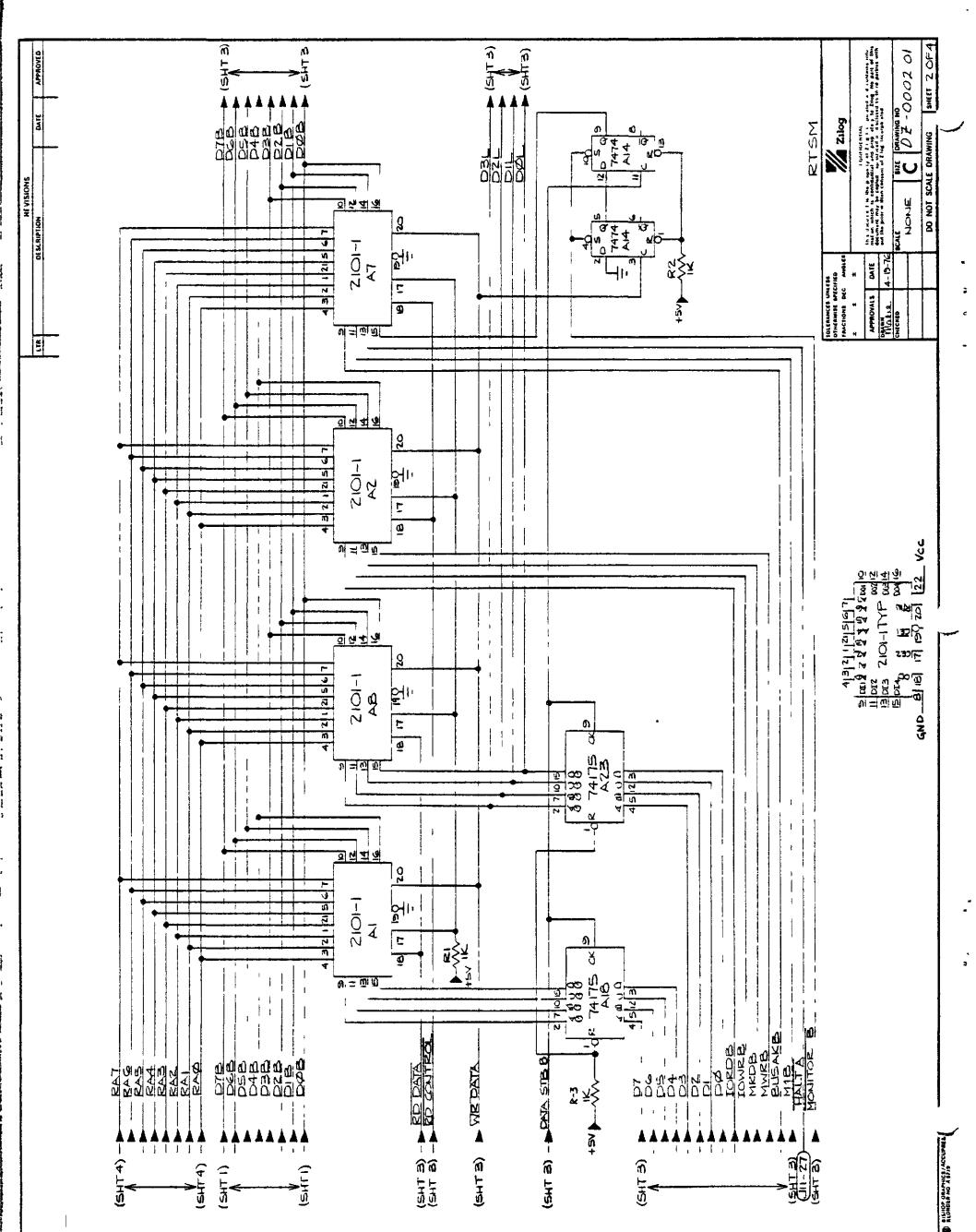

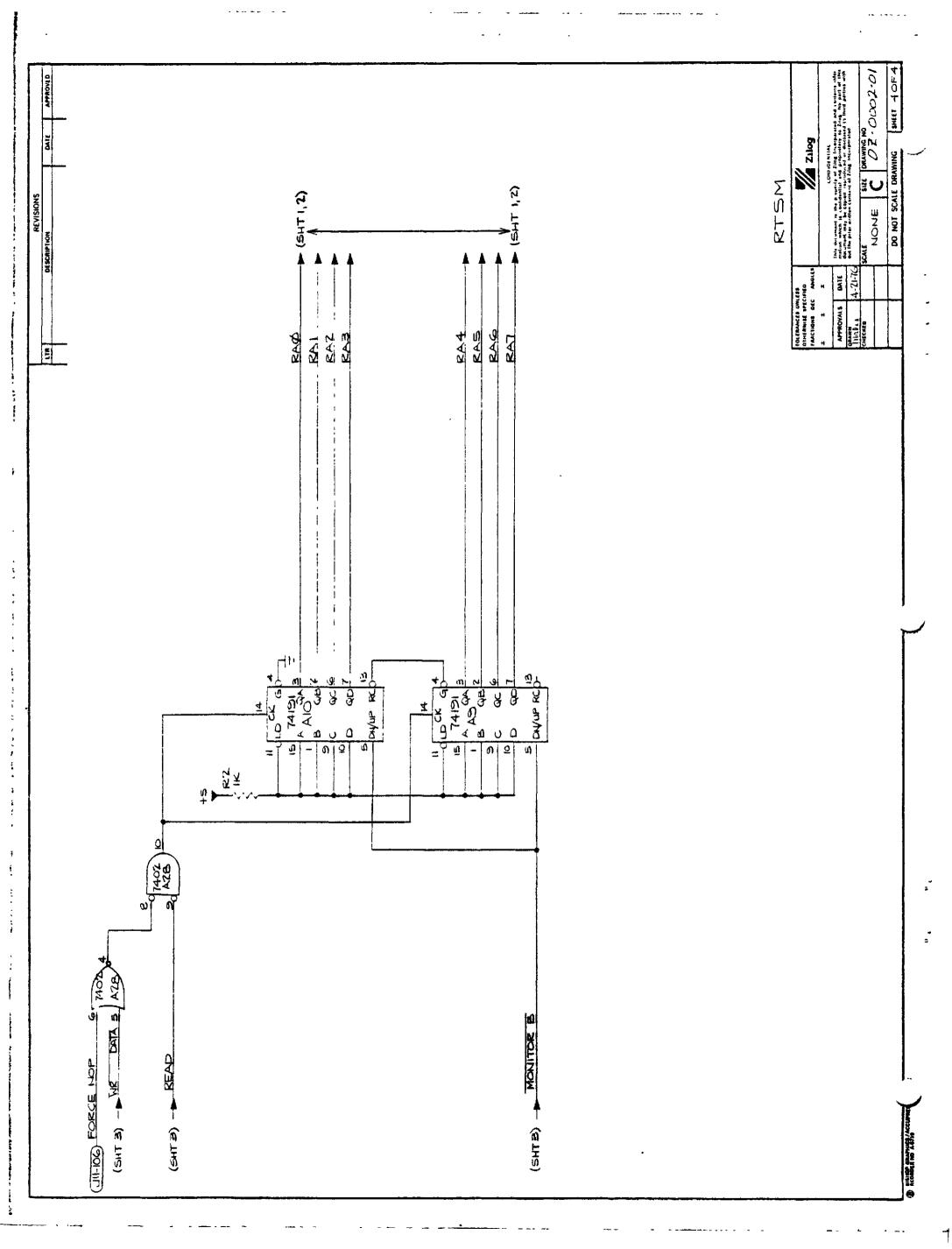

| 4.6    | Realtime Storage Module               | 4-56 |

|        | Storage Array (Sheet 1 and 2)         | 4-56 |

| 4.6.2  | Address Latches (Sheet 1)             | 4-56 |

|        | Data Latches (Sheet 2)                | 4-58 |

|        | Control Decode (Sheet 3)              | 4-58 |

|        | Data Bus Drivers (Sheet 3)            | 4-58 |

|        | Storage Control Logic (Sheets 2,      |      |

|        | 3 and 4)                              | 4-59 |

.

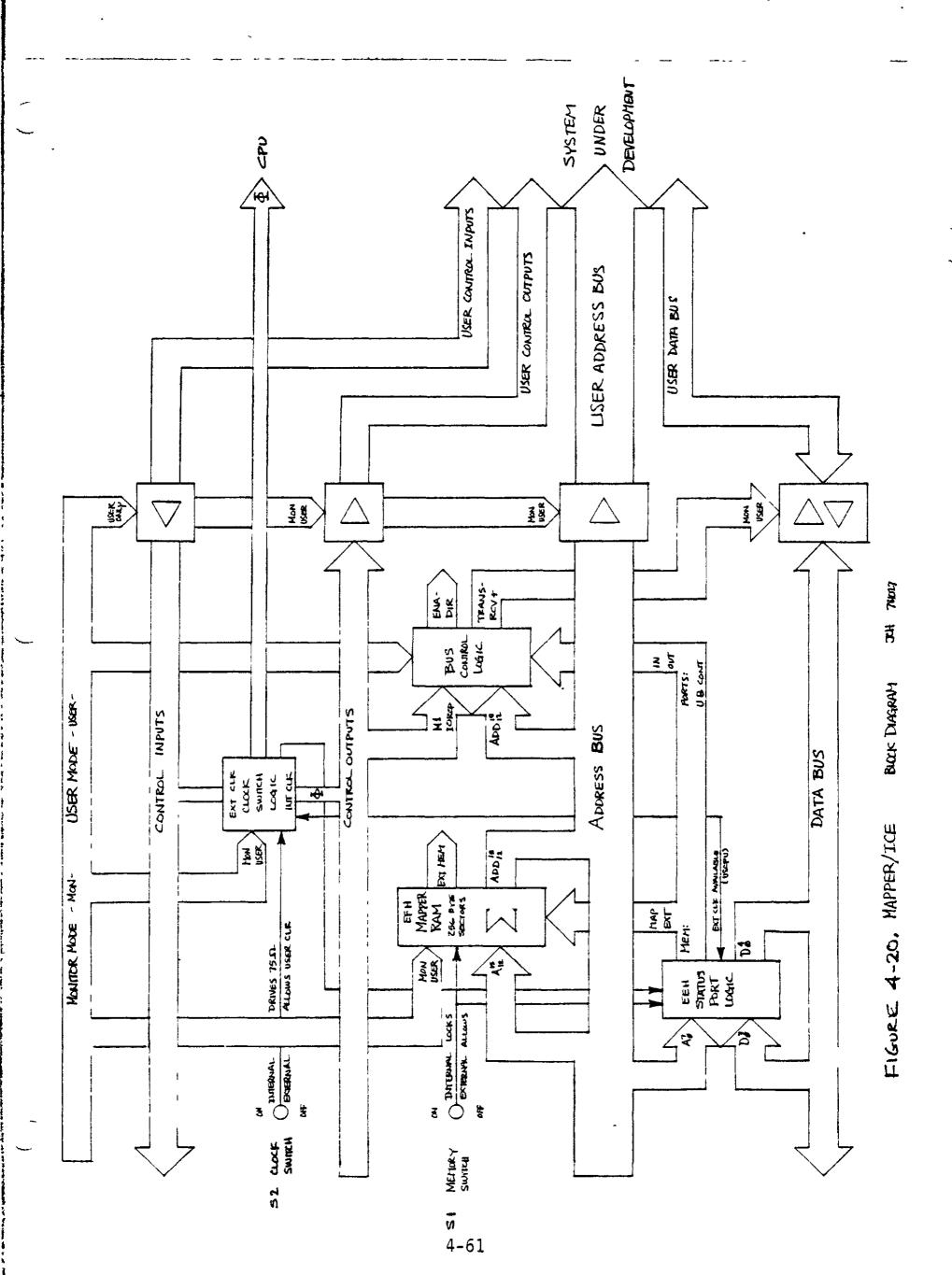

| 4.7.1 Addre<br>4.7.2 Memor<br>4.7.3 Addre<br>4.7.4 Outpu<br>4.7.5 Input<br>4.7.6 Data                                                                                                    | er/ICE Module                                                                                                                                                                                                                                                            | 4-60<br>4-60<br>4-62<br>4-62<br>4-62<br>4-63                                 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|

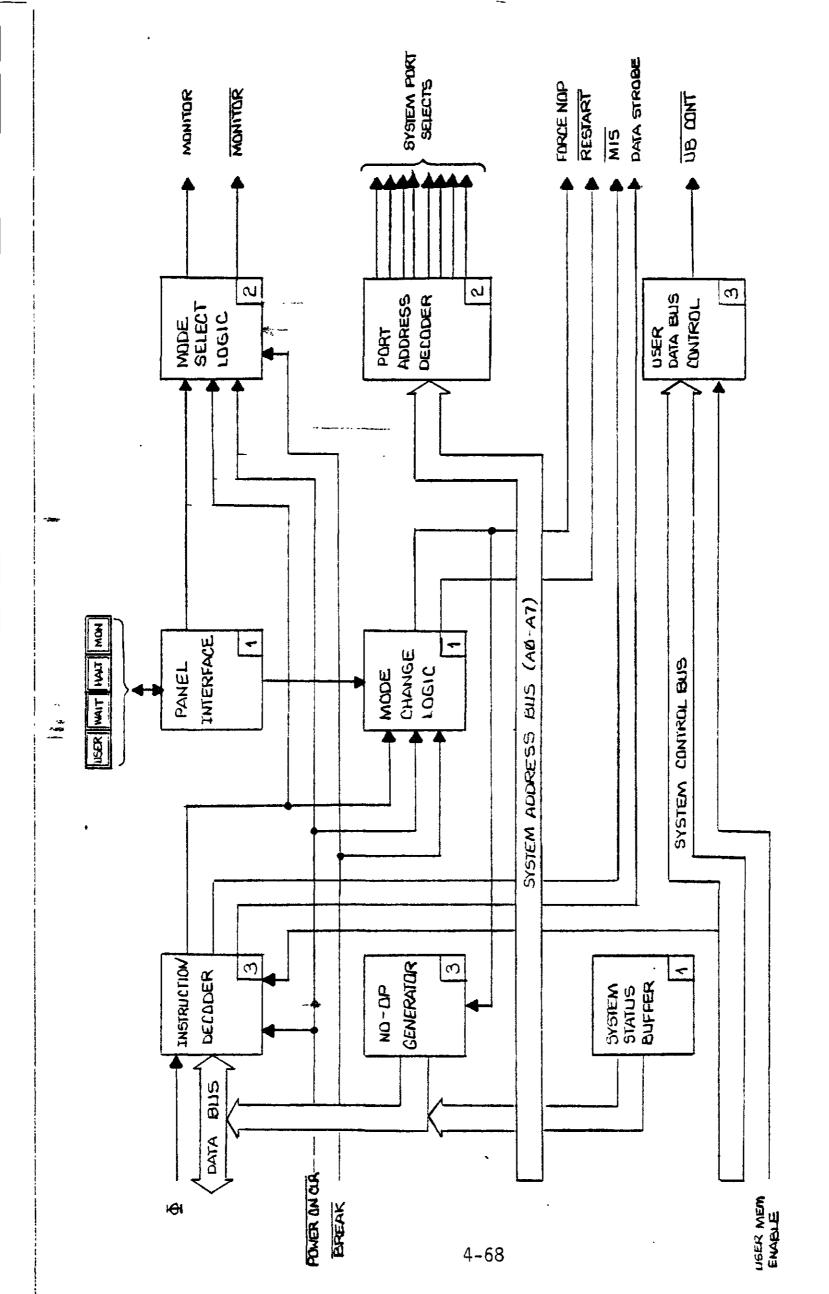

| 4.7.8 Exter<br>4.7.9 Exter<br>4.8 Monit<br>4.8.1 Panel<br>4.8.2 Instr<br>4.8.3 Mode<br>4.8.4 NO-OF<br>4.8.5 Mode<br>4.8.5 Mode<br>4.8.6 Syste<br>4.8.7 Port<br>4.8.8 User<br>4.8.9 Conso | Inal Memory  Inal Clock  Interface (Sheet 1)  Cuction Decoder (Sheet 3)  Change Logic (Sheet 1)  Generator (Sheet 3)  Select Logic (Sheet 2)  Em Status Buffer (Sheet 1)  Address Decoder (Sheet 2)  Data Bus Control (Sheet 3)  Ole Interface Receivers/  Ers (Sheet 4) | 4-63<br>4-63<br>4-64<br>4-67<br>4-67<br>4-69<br>4-69<br>4-70<br>4-70<br>4-71 |

|                                                                                                                                                                                          |                                                                                                                                                                                                                                                                          |                                                                              |

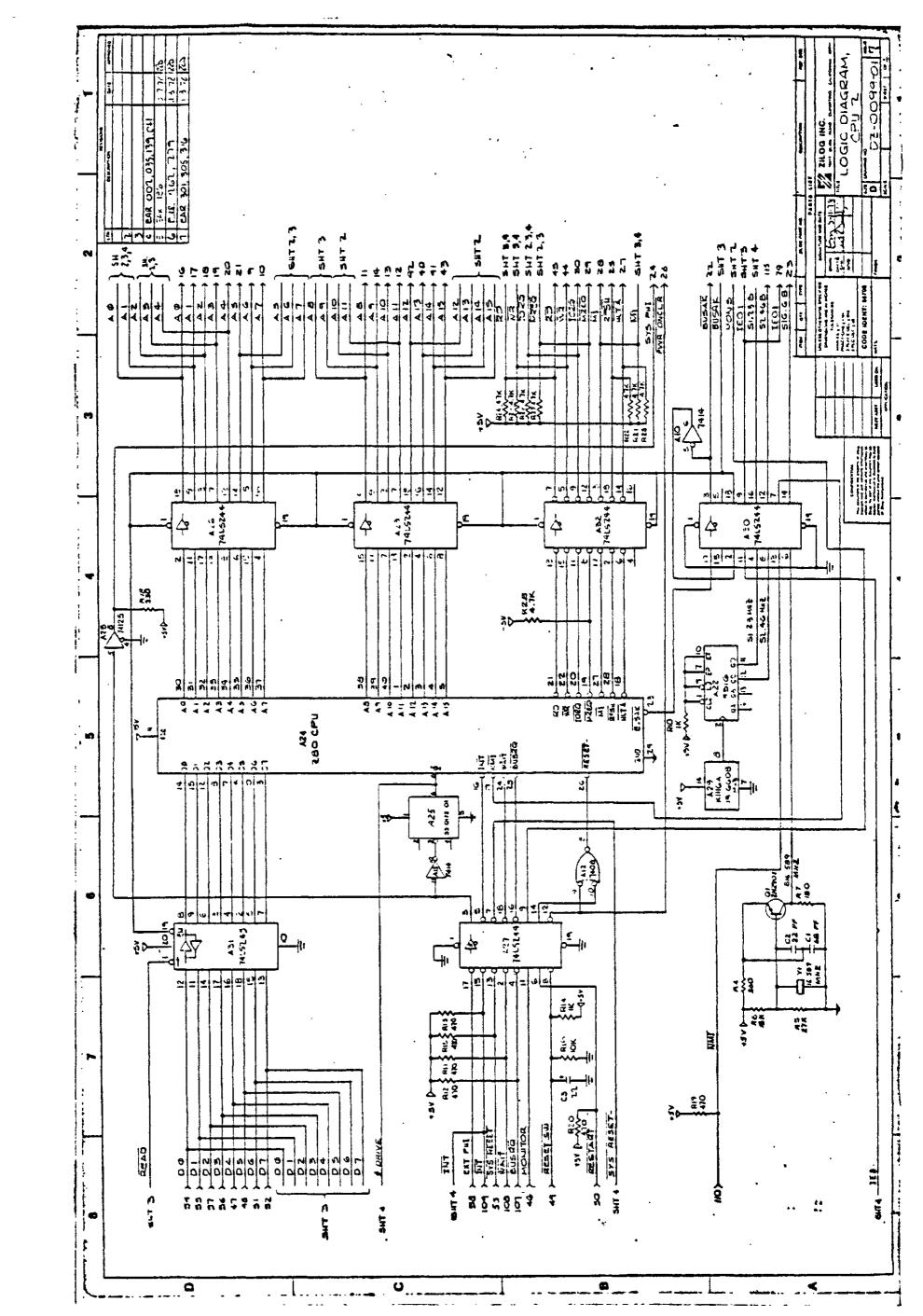

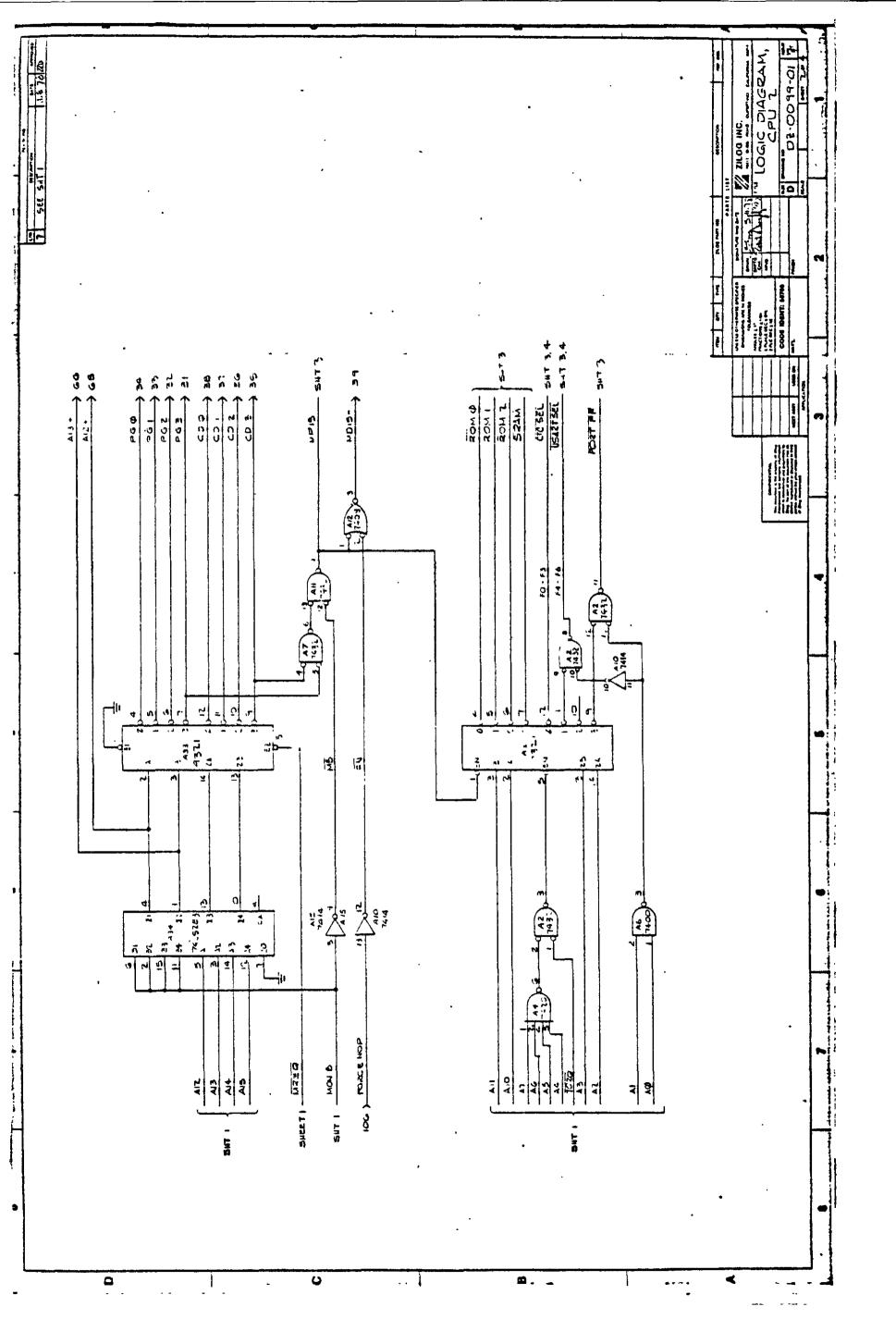

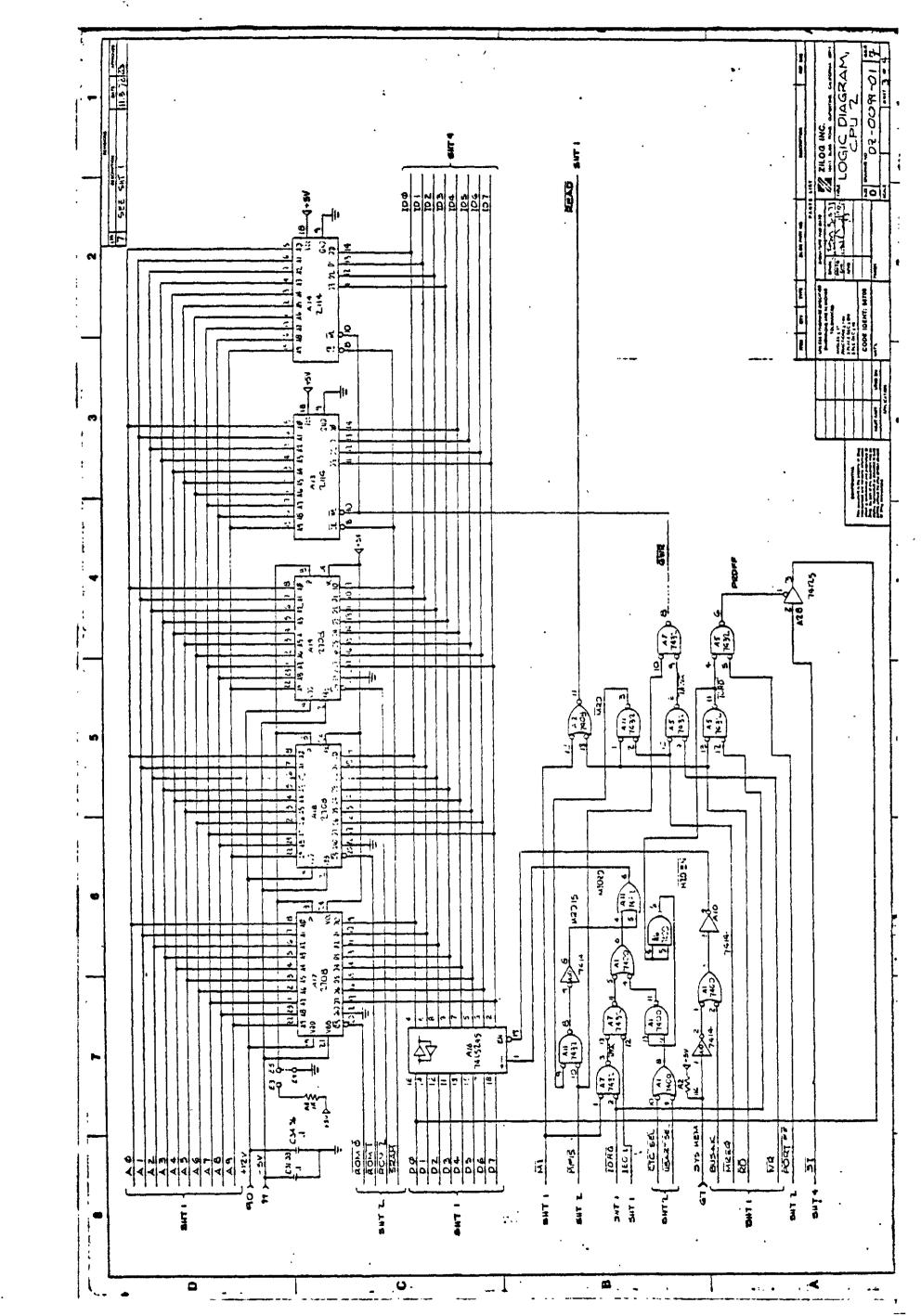

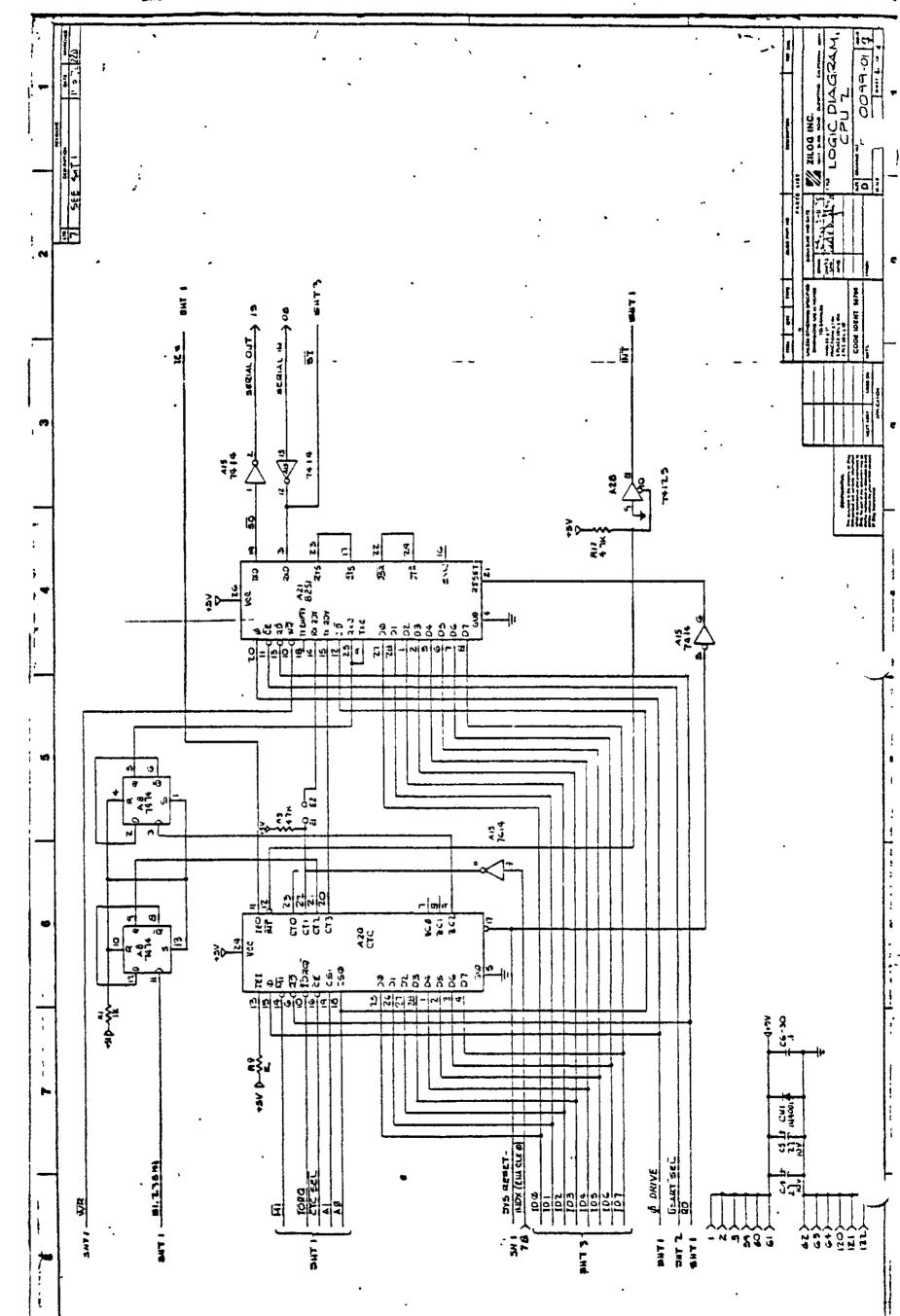

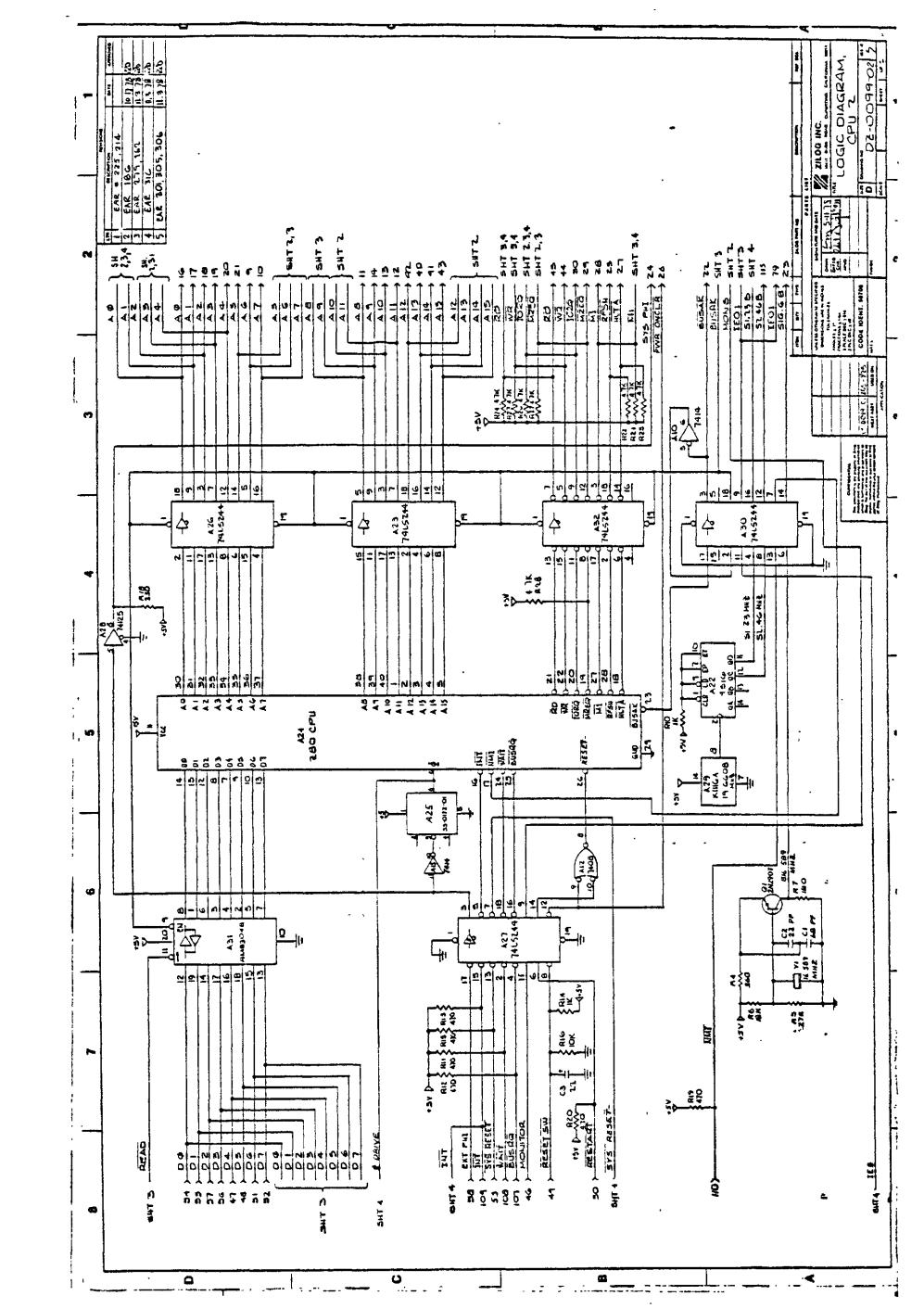

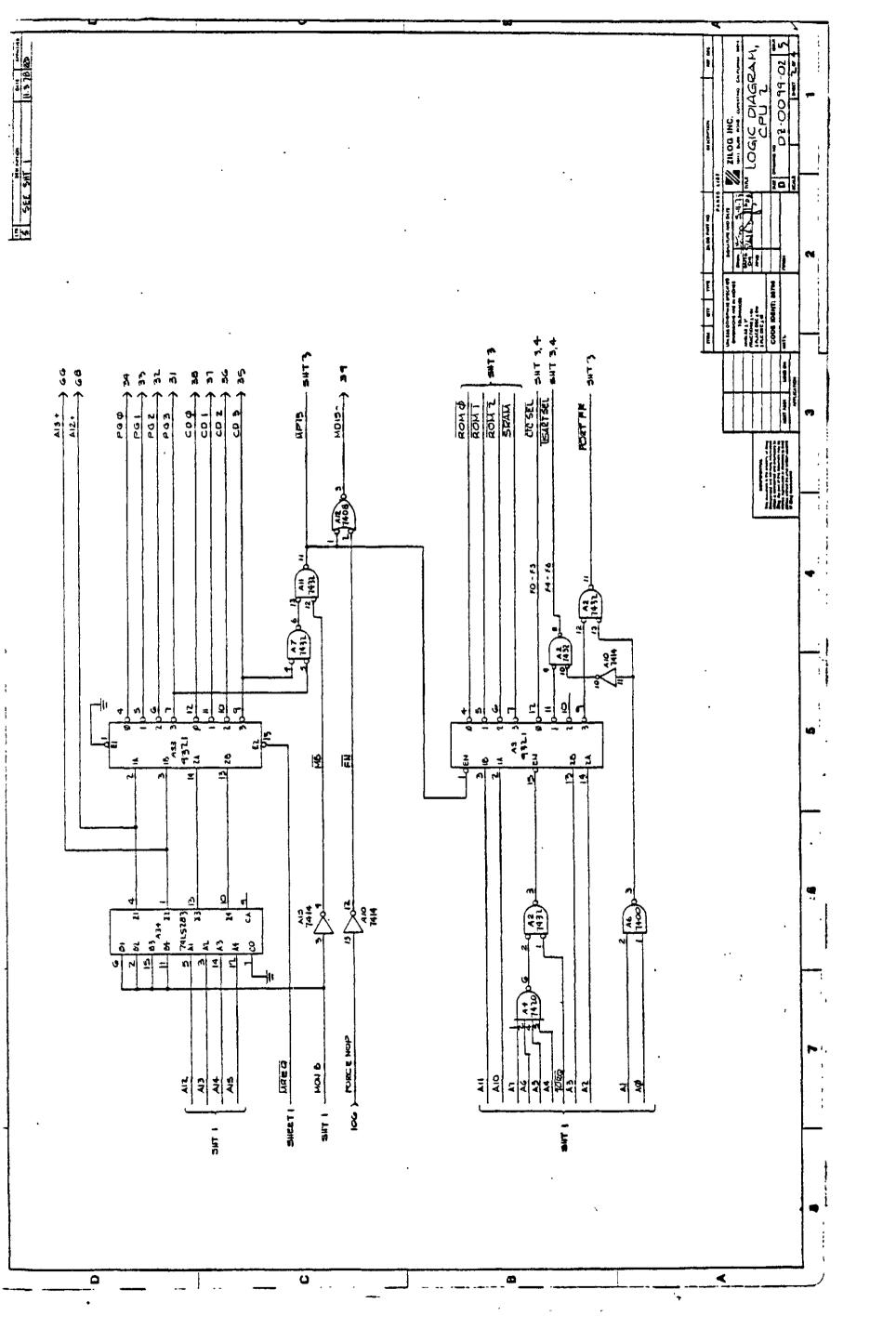

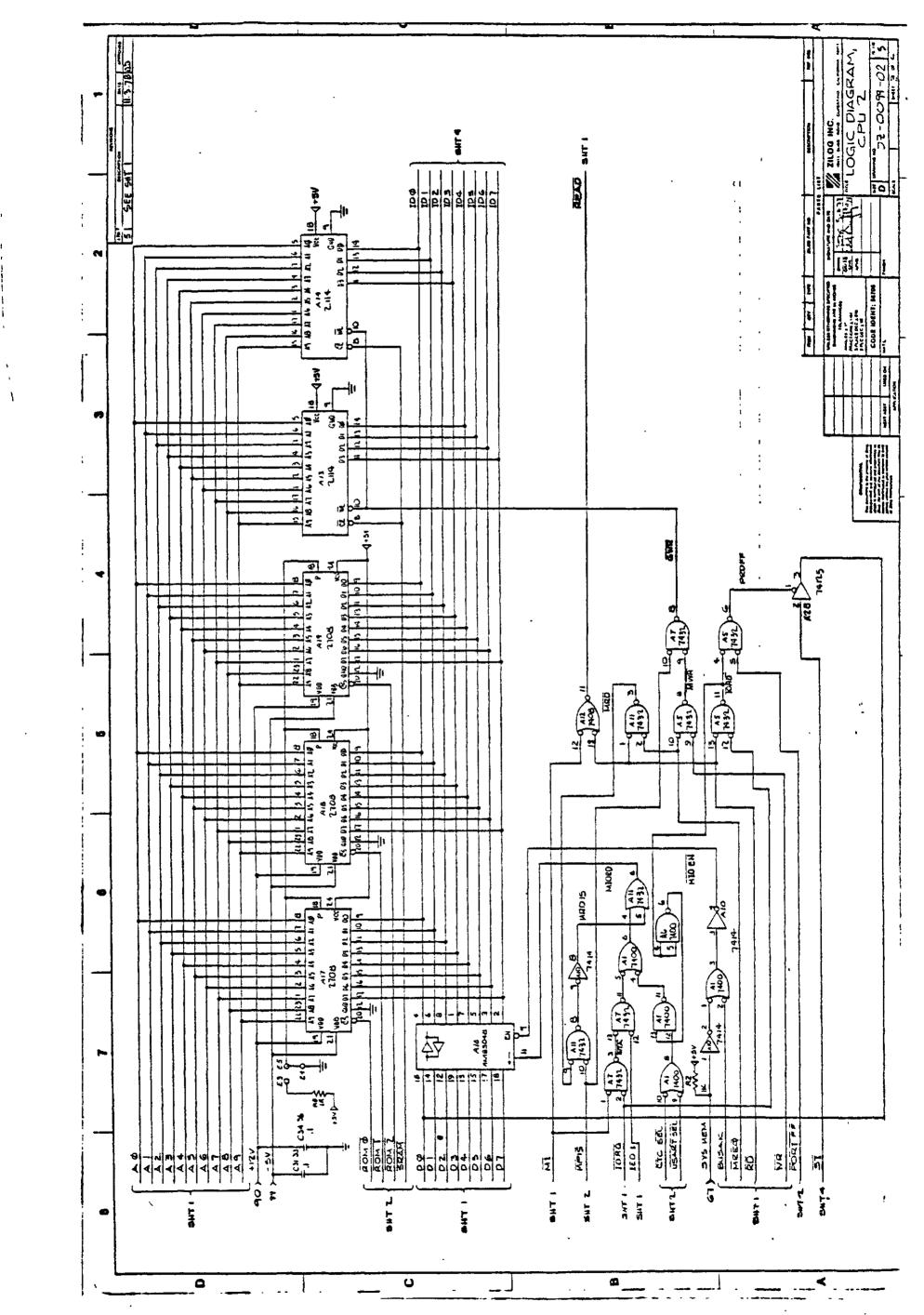

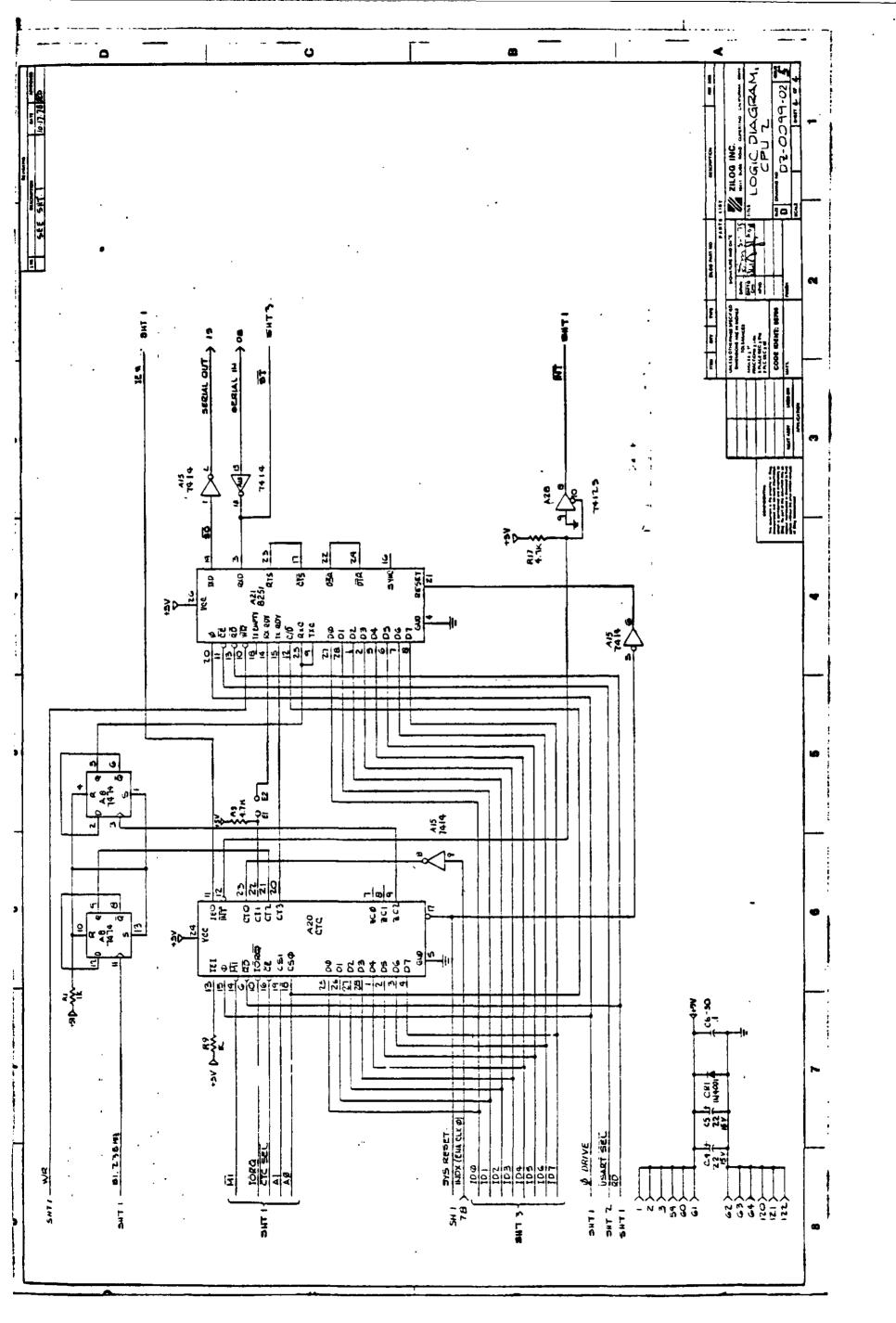

| Appendix                                                                                                                                                                                 | CPU Schematics (4 sheets)                                                                                                                                                                                                                                                | A-1                                                                          |

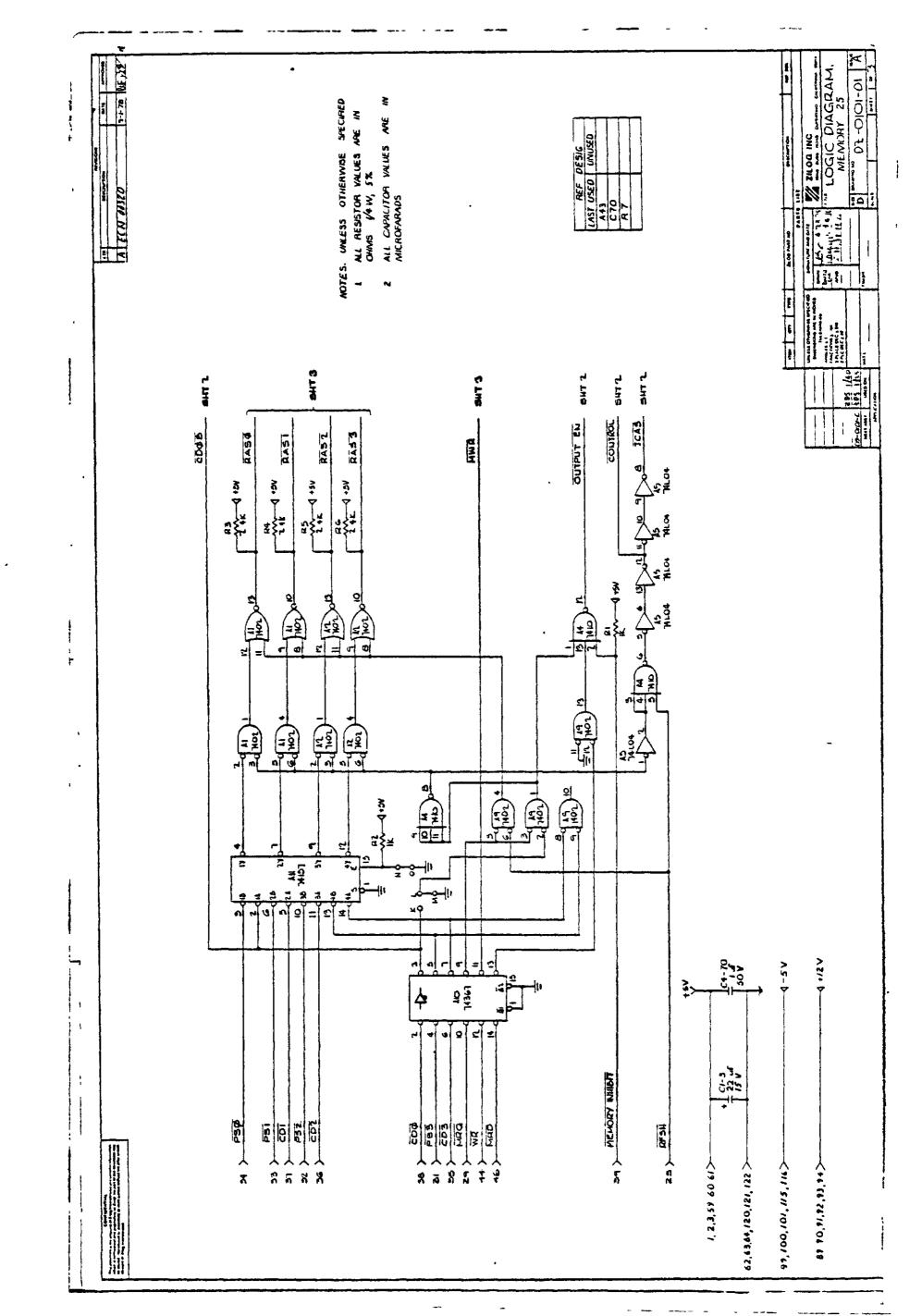

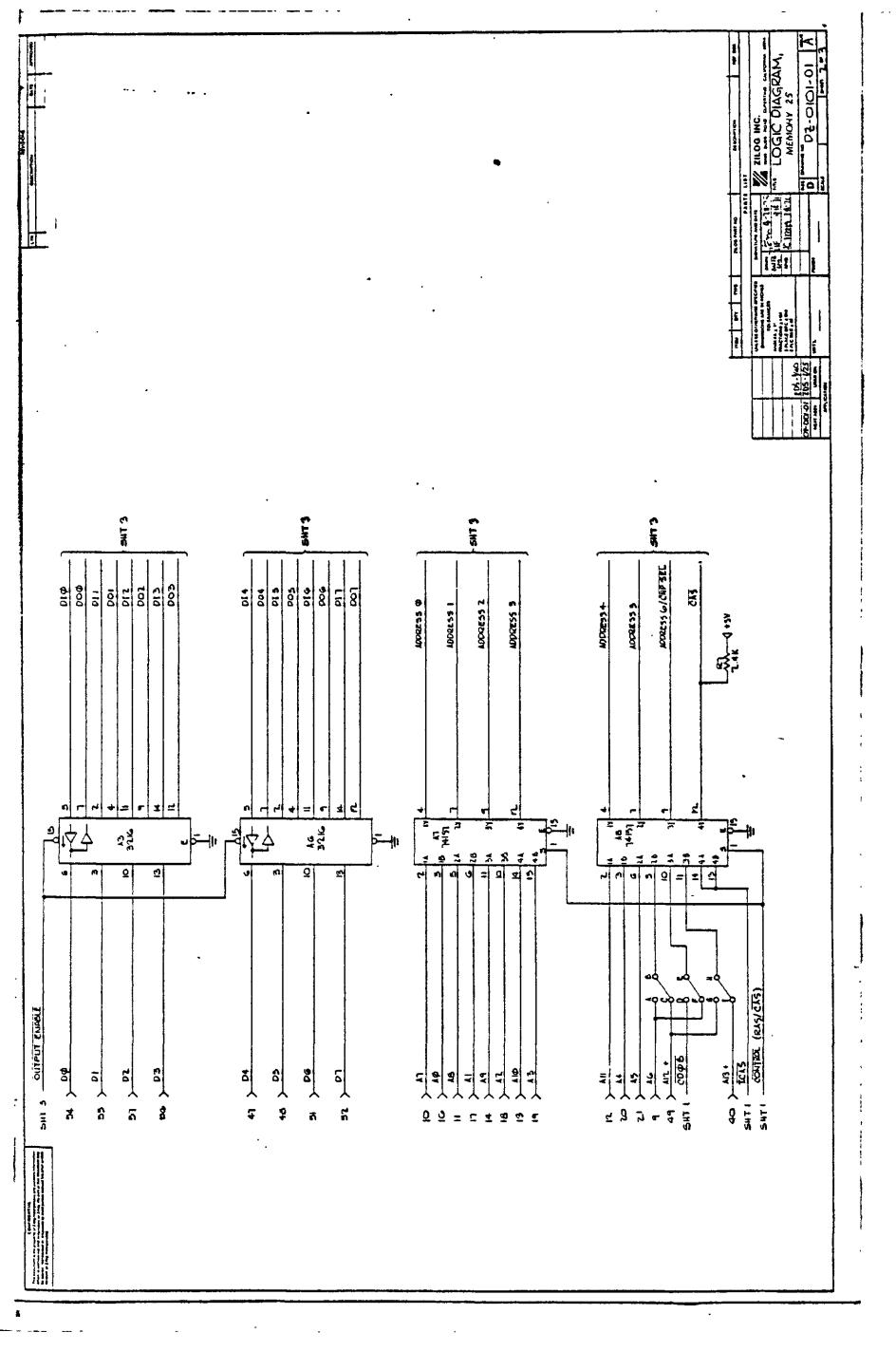

| Appendix B                                                                                                                                                                               |                                                                                                                                                                                                                                                                          | B-1                                                                          |

| Appendix C                                                                                                                                                                               | Floppy Disk Controller Schematics (7 sheets)                                                                                                                                                                                                                             | C-1                                                                          |

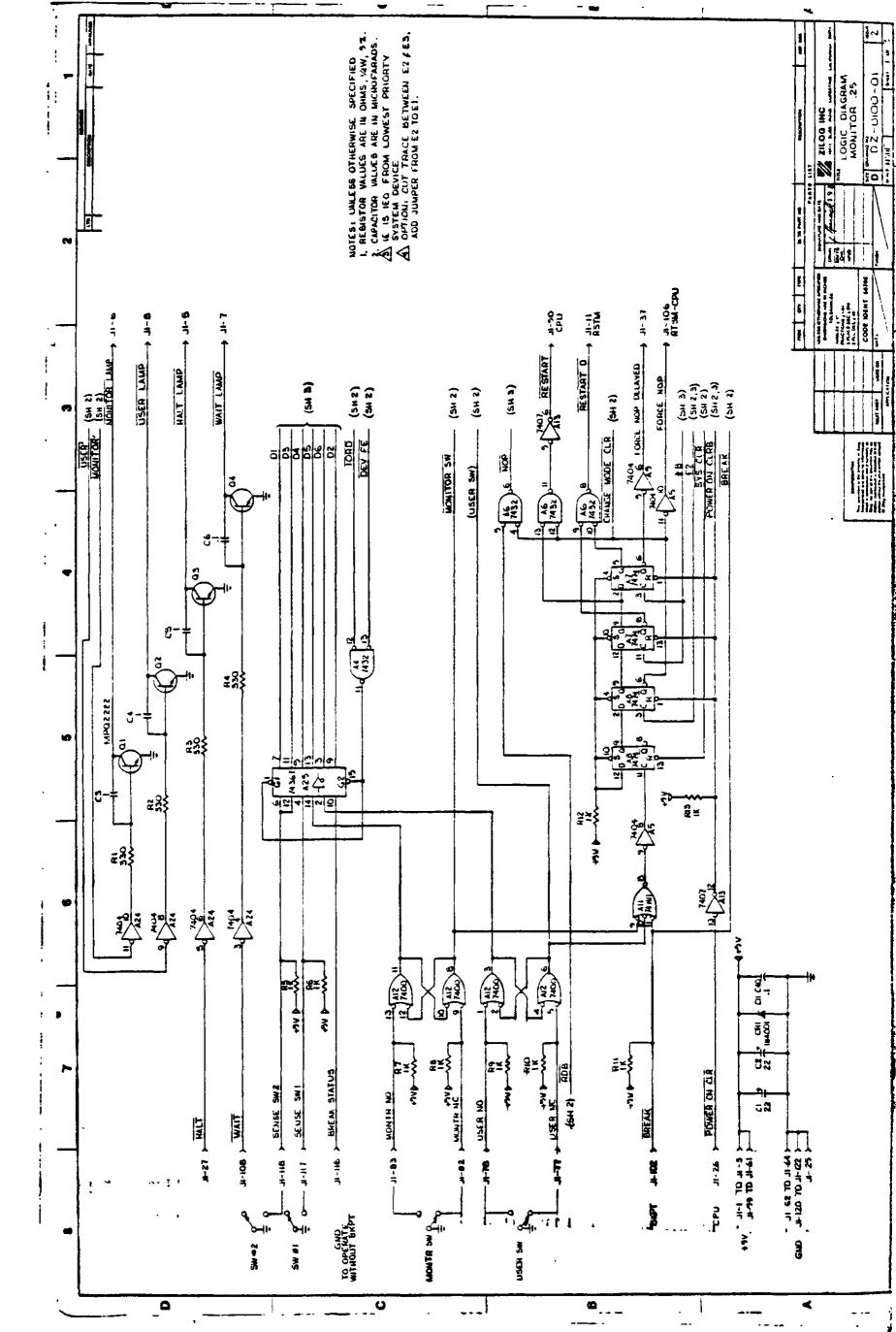

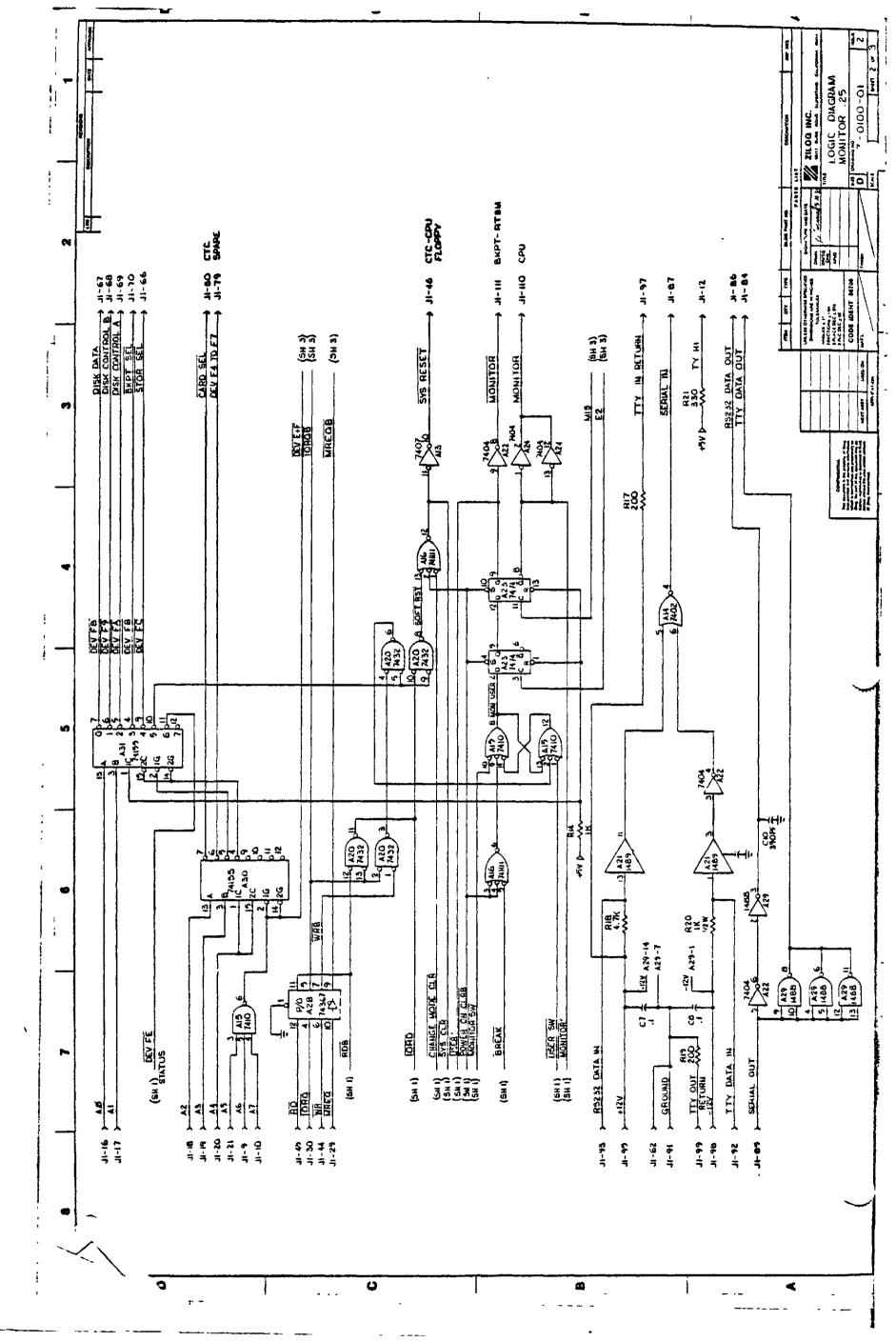

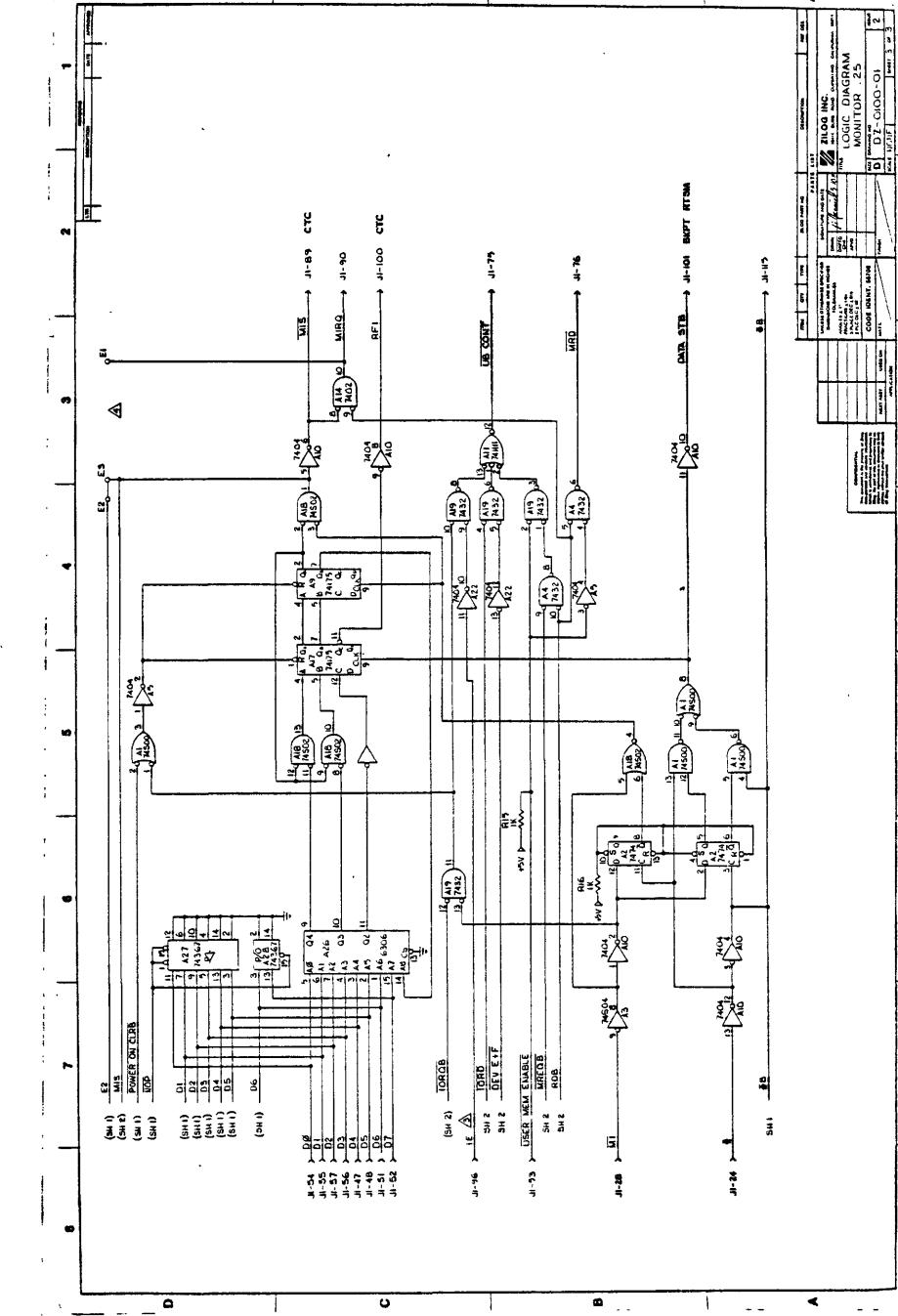

| Appendix D                                                                                                                                                                               | Monitor Schematics (3 sheets)                                                                                                                                                                                                                                            | D-1                                                                          |

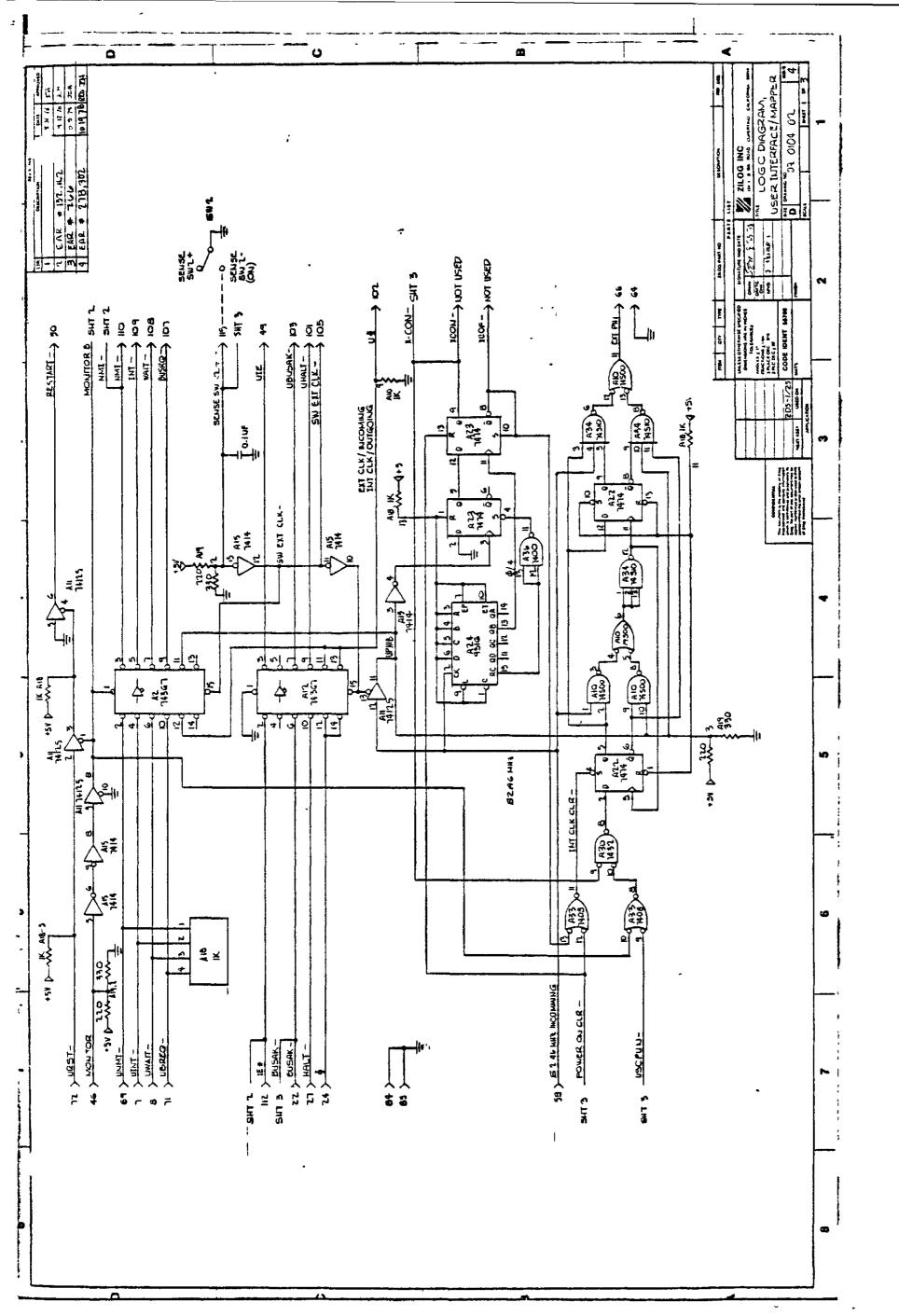

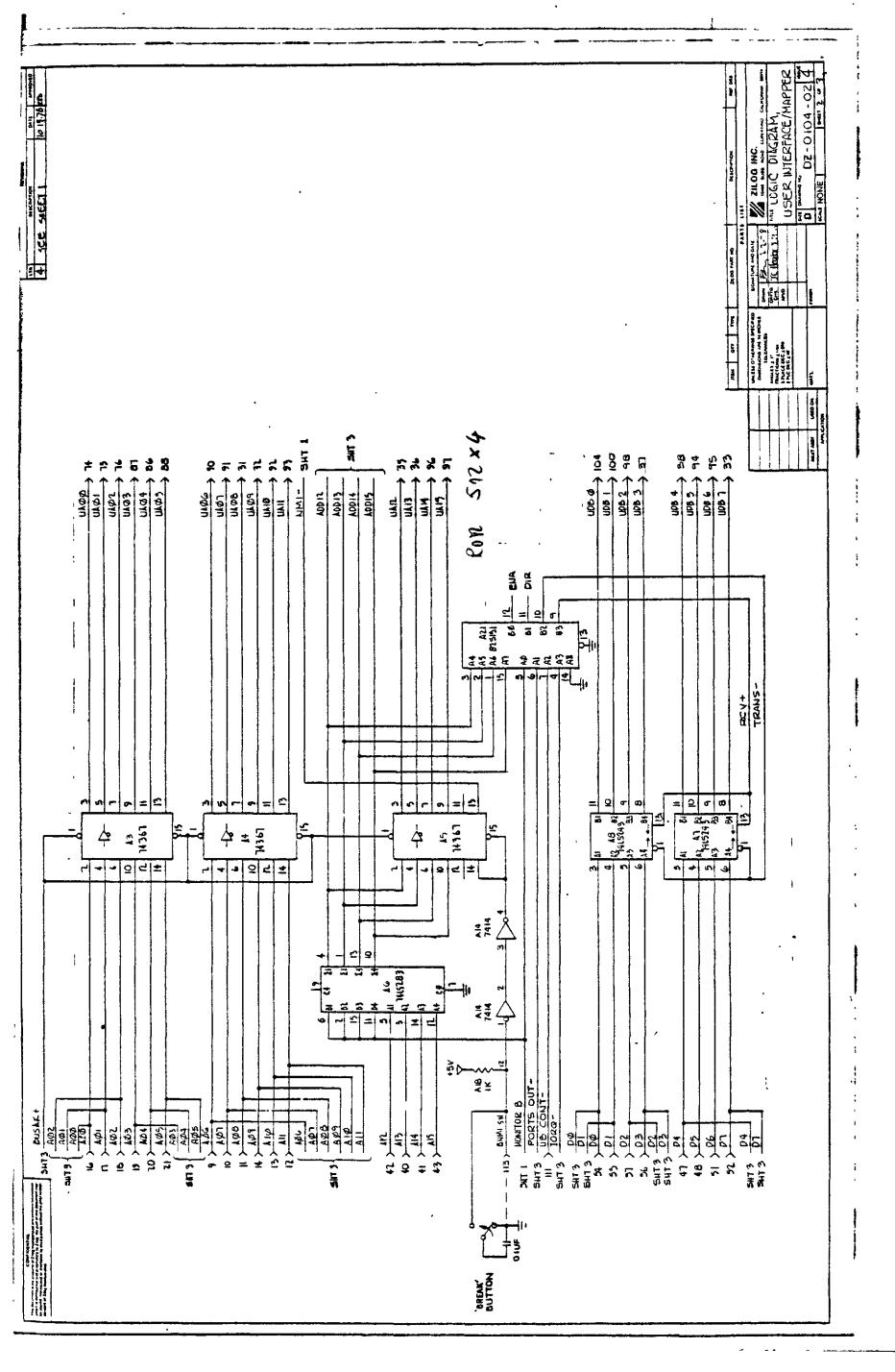

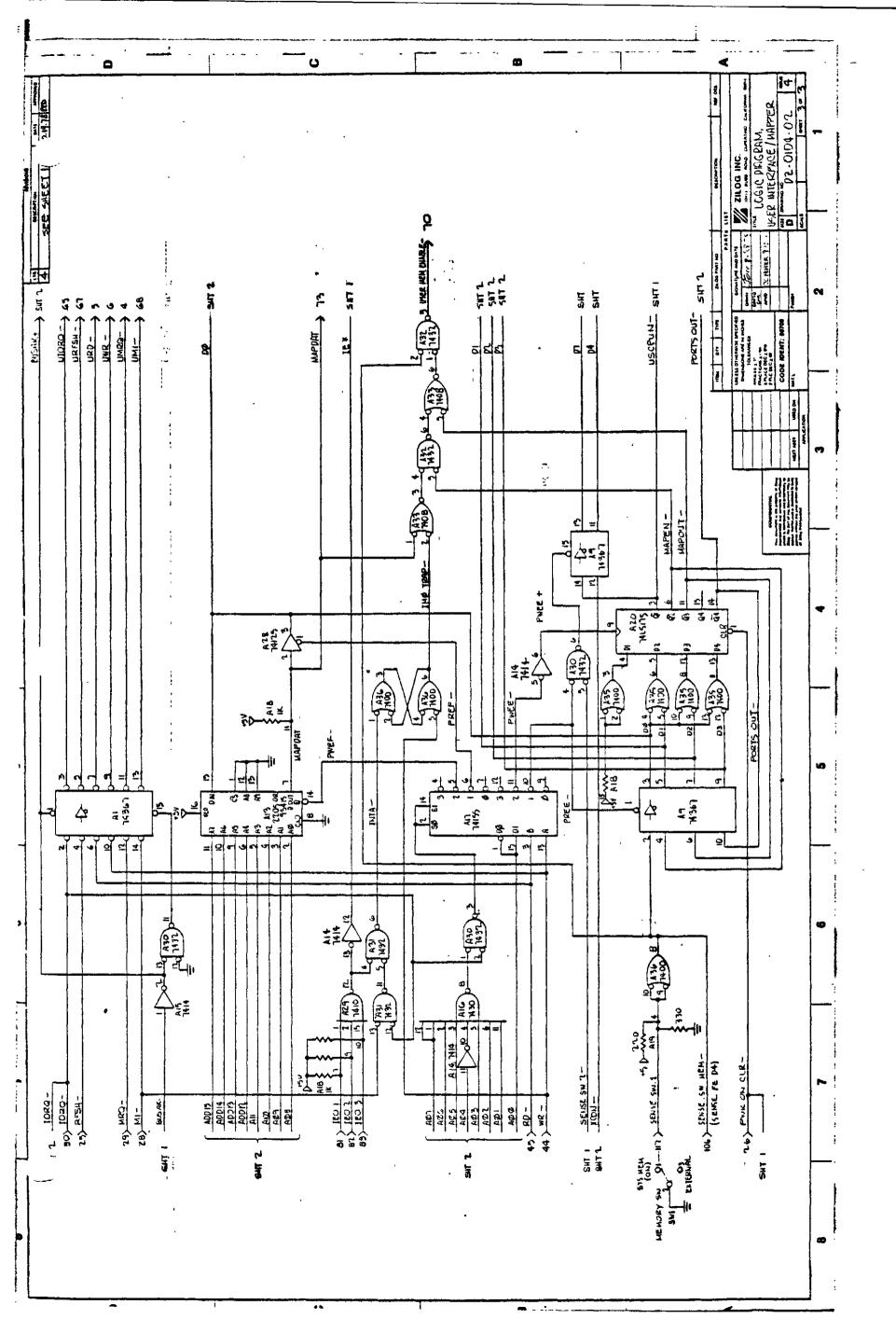

| AppendixE                                                                                                                                                                                | User Interface/Mapper (3 sheets)                                                                                                                                                                                                                                         | E-1                                                                          |

| Appendix F                                                                                                                                                                               | Breakpoint Schematics (5 sheets)                                                                                                                                                                                                                                         | F-1                                                                          |

| Appendix G                                                                                                                                                                               | Real Time Storage Module<br>Schematics (4 sheets)                                                                                                                                                                                                                        | G-1                                                                          |

| Appendix H                                                                                                                                                                               | PCB Locations for ZDS-1/25                                                                                                                                                                                                                                               | H-1                                                                          |

| Appendix I                                                                                                                                                                               | Backplane Definition, ZDS-1/25                                                                                                                                                                                                                                           | 1-1                                                                          |

**J-1**

Appendix J Pinout Charts

.

## 1.0 INTRODUCTION

## 1.1 General Information

This manual describes the installation and hardware operation of the ZDS-1/25 Development Systems. It is divided into sections to enable the user to quickly locate information pertinent to the product's installation, operation and use. The sections and their contents are shown below.

| SECTION I - INTRODUCTION             | Describes the organization of<br>the manual, related documents<br>and functional description.       |

|--------------------------------------|-----------------------------------------------------------------------------------------------------|

| SECTION II - INSTALLATION            | Describes the hardware instal-<br>lation and checkout of the<br>system.                             |

| SECTION III - MAJOR UNITS            | Describes the functional pur-<br>pose and operation of the var-<br>ous sub asssemblies in the unit. |

| SECTION IV - PRINCIPLES OF OPERATION | Describes the detailed operation of the unit as a sys-tem.                                          |

# 1.2 Related Documents

The following list of documents will provide detailed information to supplement this manual.

- RIO Operating System-User's Manual

- RIO Text Editor-User's Manual

- RIO Assembler and Linker-User's Manual

- ZDS-1/25, ZDS-1/40 PROM User's Manual

- Z80-CIB Hardware User's Manual

- Z80-ZDSP Hardware User's Manual

- Z80-PPB Hardware User's Manual

- Z80-PPB/16 Hardware User's Manual

# 1.3 General Description

The ZDS-1/25 Development System is a microcomputer system designed to support all hardware and softwre development activities for the Z80-CPU. The system includes a single cabinet which contains dual single-density hard-sectored floppy disk units, emulation interface, real-time storage module, breakpoint module, memory module, console interface module, monitor module, DC power supplies, internal cabling and single card slot for option expansion.

Specific features of the ZDS-1/25 Development System include:

- Z80-CPU with 4k bytes dedicated static RAM/ROM.

- RS-232 or current loop interface supporting transmission rates from 50-9600 baud.

- 60k bytes of dynamic RAM.

- Programmable hardware breakpoint module.

- Programable real-time event storage module.

- In-circuit emulation interface to user's prototype system.

- Memory mapping in blocks of 256 bytes.

- Dual single-density hard-sectored floppy disk drives and controller.

- Full operating system software:

- -ROM-based debug software

- -Relocatable Macro Assenbler and Linker

- -Text Editor

- -Disc File Management System

- Optional interfaces:

- -Auxiliary Serial/Parallel Input/Output Board

- -Printer Interface/Prom Programmer Interface

- -EPROM/Bipolar PROM Programmers

- -Parallel Interface Board

- Optional Peripherals ·

- -1920 character CRT terminal with upper/lower case keyboard

- -120 character/second Matrix Printer, bidirectional with forms length selector.

- Optional Software:

- -Basic Interpreter, including both binary and BCD math.

- -FORTRAN IV based on ANSI 1966 standard.

- -PLZ programming languages (Complier, Interpreter and high level assembler)

### 1.4 OPERATING MODES

Because the Z80-CPU is shared by both the system and the user's prototype during emulation, two distinct modes of operation are provided for the user. These modes of operation are clearly indicated by the MONITOR and USER switch/indicators on the front of the system.

#### MONITOR MODE:

This is the normal operating mode of the system when not using the emulation logic. In this mode all system resources are allocated to the development system and the emulation logic is disabled. While running in this mode the breakpoint module is disabled, and loading of the breakpoint module and the realtime storage parameters is enabled. The user memory in the prototype system may be accessed by the development system in part or as a whole depending on the memory mapper configuration.

#### USER MODE:

This mode is used when running in-circuit emulation and may be established in one to two fashions: (1) by pressing the USER button, or (2) by executing a Go command from the Debug environment. In this mode the Z80-CPU is dedicated to the emulation logic and is used to execute user's program in a real time mode. In order to accomplish this, certain system functions and emulation functions must occur. These functions are listed below:

- Breakpoint logic is enabled to compare address, data and control busses for equivalence.

- Breakpoint parameters may not be loaded.

- Real Time Storage Module is allowed to trace bus events.

- Real Time Storage Module parameter loading is disabled.

- Enable data strobe for Real Time Storage Modules.

- Enables Z80-CPU to see interrupt, non-maskable interrupt,

wait, bus request and reset inputs from the user's system.

- Allows user's system to utilize blocks of or the entire development system memory, save F000H-FFFFH.

- Write protects the 1K static RAM scratch pad.

#### 2.0 INSTALLATION

## 2.1 Unpacking

Each ZDS-1/25 Development System is shipped in a padded shipping container for protection. Upon receiving the system, place container in upright position, open container, remove top section of packing material, and visually inspect the unit for damage.

#### WARNING

The approximate weight of the unit is 65 lbs; exercise caution when removing unit from shipping container.

Remove the unit from the bottom of the shipping container. Insure power cable and emulation cable w/terminator are included in the container.

Remove foam pads from floppy disk units, and inspect openings for foreign objects.

Remove the two top cover retaining screws (reference Fig 2-3) from the rear of the unit, and remove the top-cover by moving it towards the rear and upward.

Inspect the inside of the unit for foreign objects, loose mechanical components, and to insure all DC power supply connections are secure.

Check all pluggable components to be sure that they are securely seated on the PC boards.

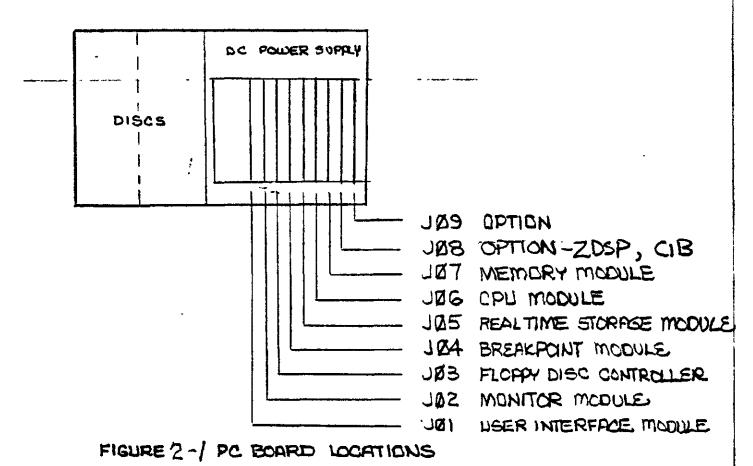

Check all PC boards to be sure that they are installed in their correct slots (reference Figure 2-1 for locations).

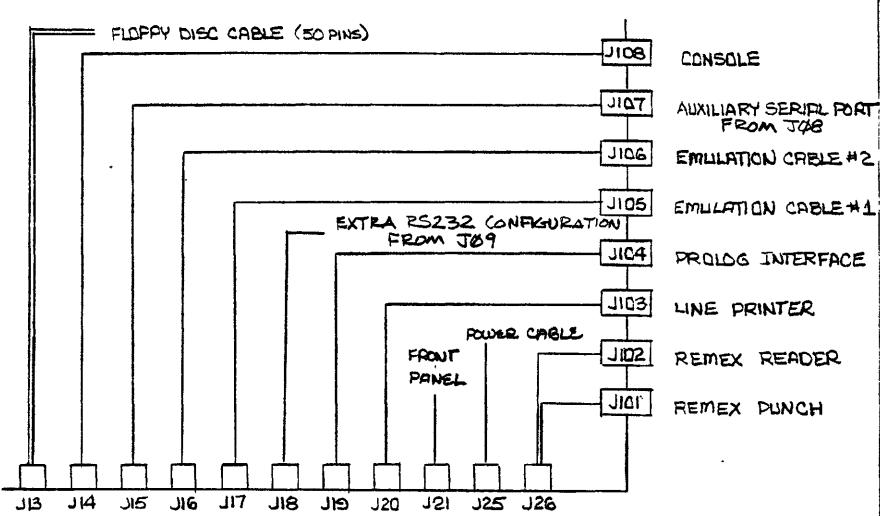

Check all I/O cable connections to be sure that they are secure on the motherboard and the rear of the unit (reference Figure 2-2).

Replace top-cover and secure with two screws, previously removed.

# 2.2 PRE-POWER CHECKS

The performance of the system can be affected by noise and/or transients entering the system on the primary power input. Therefore, one of the following noise isolation techniques should be used.

FIGURE 2-2 I/D CONNECTIONS

- a. Power-line shielding may be utilized, enclosing the input power lines in rigid conduit or metallic shielding, which is connected to earth ground.

- b. Line filters may be utilized to reduce the amplitude of transients on the line.

#### GROUNDING

The proper grounding of the system is extremely important, especially when connecting the emulation cable to the user's prototype system. Inadequate grounding often causes intermittent problems which may be difficult to isolate. Also, inadequate grounding between the prototype and the development system may result in damage to the emulation interface and/or user's prototype.

All Zilog machine power cords contain an insulated equipment ground wire (green, or green with yellow stripe), which is indentical in size and insulation to the grounded and ungrounded supply conductors. This conductor connects the machine frame ground to a protective ground on the input power plug.

### WARNING

An insulated grounding conductor identical in size and insulation to the grounded and ungrounded branch-circuit supply conductors, except that it is green or green with one or more yellow stripes, is to be installed as part of the branch-circuit that supplies the unit. This conductor must be connected at the service equipment. Conduit must not be used as the only grounding medium.

#### PRIMARY INPUT POWER

Prior to connecting the power cable between the input power source and the system, the source must be checked for proper polarity, voltage and grounding.

Cycles (+/- 1%:) 60HZ 50HZ

Phase: Single Single

Voltage (+/- 10%) 110VAC 100/230 VAC

Current:

### 2.3 CONSOLE CONNECTION

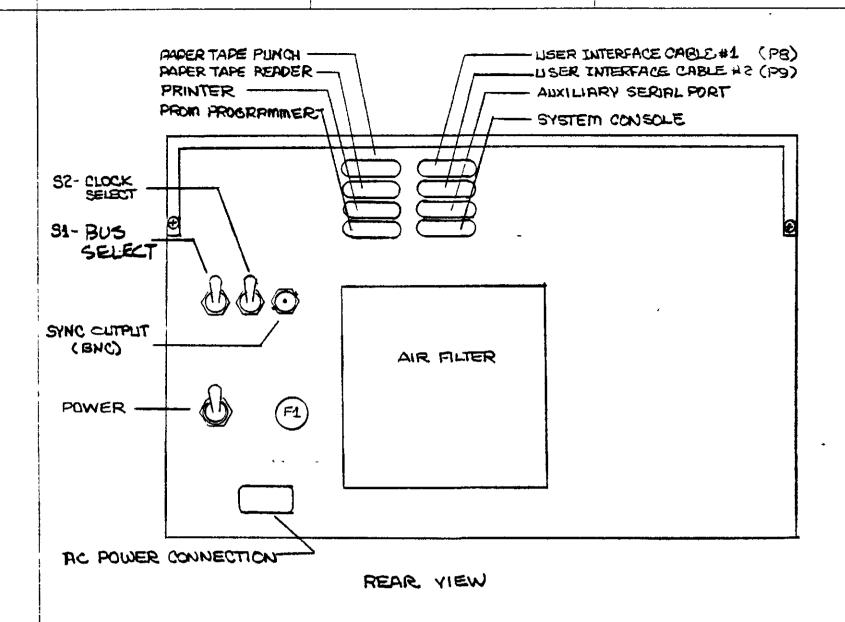

A single 25-pin female connector is provided at the rear of the unit for connecting a console driver (reference Figure 2-3). The console device may be any keyboard printer or CRT display device employing an RS-232 or 20 ma. current loop interface. Baud rates for the console may be from 50-9600.

#### CAUTION

The terminal connector on the rear of the system is shipped with pins 5,6 and 8 wired high. According to standard RS-232 specifications, these pins are designated:

Pin 5-Clear to Send Pin 6-Data Set Ready Pin 8-Carrier Detect

These pins serve as TTY.RETURN lines which are pulled up to +12v through 200 ohms.

The only pins used by the RS-232 interface are:

Pin 2-RS232 Data In Pin 3-RS232 Data Out Pin 7-RS232 Return

Pins used by the current loops (teletype) interface are:

Pin 10-TTY Data In Pin 16-TTY Data Out Pins 5,6,7,24-TTY IN Return Pin 17-TTY Out Return

After insuring that correct pin connections exist in the cable from the terminal, the cable may be connected to the terminal connector on the rear of the unit.

### 2.4 POWER UP SEQUENCE

Apply power to terminal console device and apply power to the ZDS-1/25 by activating the switch on the rear of the unit. The MON indicator should be illuminated and the fan should energize.

FRONT VIEW

Figure 2-3 ZDS-1/25 DEVELOPMENT SYSTEM

-•

.

.

•

.

## 3.0 MAJOR UNITS

### 3.1 General Information

The ZDS-1/25 contains the basic hardware of a microcomputer system, plus an emulation subsystem used for real-time hardware and software debugging (reference Figure 3-1). The various modules that comprise the system will be described functionally, concentrating on their inter-relationship and the role they perform in the overall system. For detailed operation of each module, reference Section 4.0 Principles of Operation.

# 3.2 Microcomputer System

The modules that compose the microcomputer system are the Central Processor Module, Dynamic Memory Module, Floppy Disk Controller Module, and the Optional I/O Modules(s). These are described in the following text with the exception of the I/O Modules which are described in seperate manuals (reference Section 1 for manual title and number).

## 3.2.1 Central Processor Module (CPU)

The Central Processor Module provides the major control for the system using the Z80-CPU. Resident on the CPU module is the 3K Monitor PROMs which serve to control all debug and emulation activity along with simple I/O drivers for the console and floppy disk interface. A lK byte static RAM memory is provided to be used as a "scratch pad" for the 3K monitor. All Z80-CPU signals are buffered on the board providing interface to the internal address, data and control busses. Decoding of address signals provides page and card select signals used by on board PROM/RAM and the off-board Dynamic Memory Module. The page and card selection forces the 3K Monitor and lK static RAM to appear at address F000-FFFFH while the system is in MONITOR mode. This feature allows the user to create and debug programs which are located at any address from 0000-EFFFH.

The CPU Card also provides the system with a USART to enable asynchronous interface with the system console device. Baud rate synchronization with the console device is automatic and rates from 50-9600 Baud are supported. Like the Floppy Disk Controller Module, the actual intelligence for this module resides in the 3K PROM Monitor. Also provided is a four-channel counter-timer circuit, Z80-CTC, which is used partially by the system and may be also controlled by the user.

## 3.2.2 Dynamic Memory Module (DMM)

A single Dymanic Memory Module is provided in the system; it contains a maximum of 60K bytes of storage when 16Kxl Dynamic RAM components are employed. All refresh timing signals are generated on board and are triggered by the refresh signal from the CPU module. Jumpers on the board allow use of either 16K or 4K memory components by controlling selected address lines received from the CPU module.

# 3.2.3 Floppy Disk Controller Module (FDC)

The Floppy Disk Controller Module provides an interface between the system and two single-density, single-sided, hard-sectored floppy disk units. Actual intelligence, which is required by the controller, is contained in the 3K Monitor PROM's located on the CPU module. The controller serves as a temporary data buffer, interface to the disks, data modulator, data separator and CRC generator and checker.

# 3.2.4 Optional I/O Modules

Optional card slots (J8 and J9) are provided for I/O expansion. Any one of the ZDS-1 Series option boards may be installed in one of these slots without modifications to the motherboard wiring. For details regarding these options reference the appropriate manual listed in Section 1.2.

#### 3.3 EMULATION SUBSYSTEM

A group of modules comprise a specialized subsystem within the ZDS-1/25. Its purpose is to monitor and control the interface between the ZDS-1/25 and the user's prototype while performing in-circuit emulation. This subsystem is composed of the following modules described in subsequent subparagraphs below.

- Breakpoint Module

- Real Time Storage Module

- User Interface Module

- Monitor Module

## 3.3.1 Breakpoint Module (BKPT)

The Breakpoint Module provides the user with a means to terminate execution of a program when specified conditions of the address, data or control bus occur. This feature is most useful when debugging programs or hardware that run in real-time. The breakpoint allows real-time execution of a program until the selected event occurs, at which time one of two events may occur: first, the user may wish to stop program execution or break on the event so that CPU registers, memory or the real-time storage module may be examined; second, the user may wish to generate a sync pulse on the occurrance of the event to trigger external test equipment to monitor the event in his own hardware. Either of these can be accomplished easily by entering the desired parameter from the system console.

The Breakpoint Module is loaded (with the parameters entered via the system console) by the 3K Monitor PROM. These parameters, called "arguments," may be any one or a combination of the following:

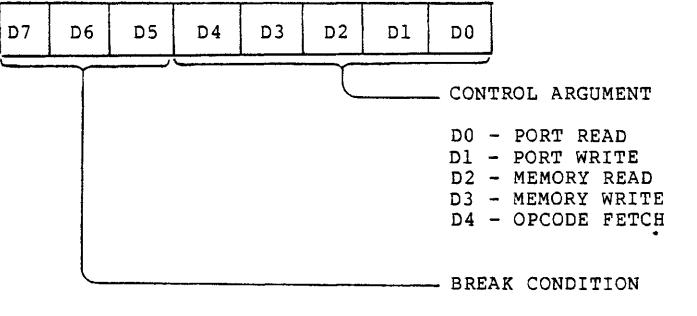

- CONTROL ARGUMENTS:

- Ml Op Code Fetch

- MR Memory Read

- MW Memory Write

- PR Port (I/O) Read

- PW Port (I/O) Write

- ADDRESS ARGUMENTS

- A Memory Address

- P Port (I/O) Address

- DATA ARGUMENT

- D Data Byte

- M Data Mask

## 3.3.2 Real Time Storage Module (RTSM)

The Real Time Storage Module provides a means for the system to store selected bus transactions while executing a program. This feature allows the system to trace address, data and control bus lines in real time execution of the user's program to provide a history of the most current 256 selected events. The user may display the contents of the history on the system console to analyze the execution of the program under test.

Control of the RTSM is provided by the emulation subsystem, (while executing the user's program) to enable real-time storage of bus activity. Parameter loading and display of the history is controlled by the 3K PROM Monitor on the CPU module. The user may select any one or a combination of the trace parameters to trace:

- Memory Reads

- Memory Writes

- Port (I/O) Reads

- Port (I/O) Writes

- All Read Operations

- All Write Operations

- All Port Operations

- All Memory Operations

- All Operations

# 3.3.3 User Interface Module (UIM or Mapper/ICE)

The User Interface Module provides the electrical interface between the emulation subsystem and the user's prototype system so that in-circuit emulation may occur. Connection between the ZDS-1/25 and the user's prototype is achieved by a three-foot cable and termination block. The M/ICE contains receivers, drivers and interface controls, as well as a memory mapper.

Memory mapping allows the user's prototype system to borrow blocks of development system memory, each block being composed of 256 bytes. Typically, this feature is used when the user is developing software that will eventually reside in PROM on the prototype. By means of the mapper, the user may borrow blocks of memory from the development system memory as though it were resident in his prototype without any degradation in system speed.

The mapper is loaded to the configuration desired by the user by executing a disk resident program called "MAPPER." Once the map is loaded, the user may enable the map or disable the map using one of the methods shown below. Control of bus access is provided by Switch One (S1) on the rear of the unit.

### TO ENABLE MAPPER LOGIC:

Place MEM select switch (S1) to map EXT (sw down) and issue a port write to EEH with data bit D1 low.

TO DISABLE MAPPER LOGIC (use one of the following):

- Place MEM select switch (S1) to internal MEM (sw up)

- Execution of Port Write to I/O Port EEH with data bit Dl high

- Operator depresses the WAIT button (System Reset)

Also provided on the M/ICE is clock selection logic, which selects the clock source for the Z80-CPU while running emulations, i.e., internal (2.5 MHZ) or external (variable). Clock selection is controlled by S2 on the rear of the unit; UP for internal, driving clock, DOWN for external clock.

# 3.3.4 Monitor Module (MON.25)

Although the monitor module provides several diskrete functions for the system, its primary purpose is to provide various strobes and controls used by the emulation subsystem. The diskrete functions provided by the monitor are as follows:

- Console Electrical Interface provides receiver and driver circuits which allow use of standard RS-232 or current loop device as the system console. The method of interface determines which receivers and drivers are employed.

- Operator Panel Interface provides debounce circuitry for the MON, USER, WAIT, Sl and S2 switches; provides lamp drivers for MON, WAIT, HALT and USER indicators; provides switch synchronization logic between modes and system logic functions to prevent undesirable disruption of system timing.

- System I/O Port Decode provides decoding logic for Z80-CPU address bits A0-A7 to select system address ports of F0-FFH and to prevent user's prototype from addressing the system I/O ports E0-FFH.

The remainder of the logic on the monitor is used to generate control signals used by the emulation subsystem to sample data, address and control busses, or to provide control of the interface to the user's prototype and synchronize the emulation subsystem to the user supplied clock if external clock is selected.

?

•

### 4.0 PRINCIPLES OF OPERATION

### 4.1 GENERAL INFORMATION

The following discussion describes the detailed operation of each p.c. board used in the ZDS-1/25 Development System. A block diagram of each board is provided, showing the various functional units on the board, which are then related to a specific logic Sheet number for further circuit clarification.

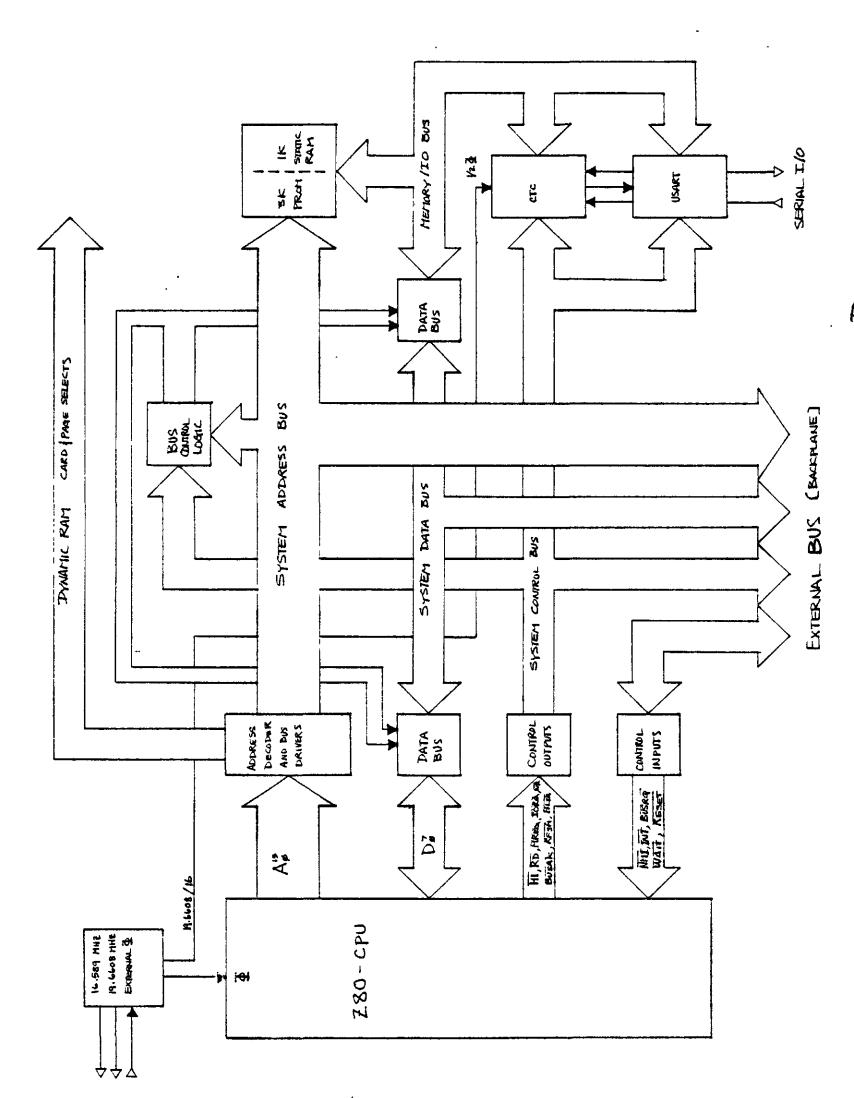

### 4.2 CENTRAL PROCESSOR MODULE

The processor card contains a Z80-CPU, Z80 CTC and USART for console interface, plus 3K of PROM and 1K of static RAM for controlling the debug environment. System PHI is derived from a 19.6608 MHZ oscillator is provided to the floppy disk controller for synchronous data separation.

The CPU bus is fully buffered to support stand alone system operation with full memory and I/O compliments.

The relationship of these elements is represented in Figure ----.

# 4.2.1 Z80 Microprocessor (Sheet 1)

The Z80-CPU serves as the control for the system. It is shared by both the system (MONITOR MODE) and the emulation subsystem (USER MODE). The Z80-CPU does not differientiate between executing programs in USER or MONITOR MODES as a consequence the surrounding logic of the microcomputer system and emulation subsystem must make the distinction. The processor operates in a normal fashion fetching and executing instructions from storage either PROM or RAM as described in the Z80-CPU Technical Manual.

### 4.2.2 Reset Logic (Sheet 1)

The Z80-CPU may be reset by one of several conditions. This reset operation will result in the following:

- Program Counter will be reset (0000H)

- Interrupt Enable flip-flop will be reset, disabling all maskable interrupts.

- Interrupt Page Address Register (I) will be cleared.

- Memory Refresh Register (R) will be cleared.

- Interrupt Mode 0 will be established.

- Address and data bus go to a high impedance state while RESET is active (logic 0). Also, all control output signals go to their inactive state.

FIGURE 4-1. CPU-2 BLOCK DIAGRAM

Reset logic circuitry is triggered by one of the following events:

- RESET SW (Reset Switch) occurs when the operator depresses the momentary switch (WAIT) on the front panel of the unit.

Debounce circuitry is provided (logic Sheet 1) via C3 and R2 on the CPU board.

- RESTART is generated from the mode change logic on the moniter module and is the result of one of the following events:

- BREAK signal from the Breakpoint Module, indicating a comparison between the argument registers and the bus activity.

- Switching between MONITOR and USER modes, either by operator pressing MON or USER buttons, or a software generated mode change from the 3K PROM Debug firmware.

- SYS RESET does not directly reset the Z80-CPU, but instead generates the RESTART signal previously described. The SYS RESET signal may be generated by (1) power-on clear signal, (2) software reset commands, or (3) mode change from MONITOR to USER or visa versa.

Two outputs are generated by the reset logic; one is applied directly to the Z80-CPU as a reset while the second output, POWER ON CLR, is applied to the User Interface Module, Monitor Module and the Option card slot as a reset.

### 4.2.3 CLOCK GENERATOR (Sheet 1)

The Z80 CPU bus buffers are shown on Sheet One of the schematics. System PHI is generated by hybrid oscillator A29. Counter A22 produces the 2.46 MHz system clock as well as half PHI for baud rate timing. The discrete circuit oscillator is controlled by a 16.589 MHz crystal and is used by the floppy controller's synchronous data separator.

Data bus buffer A31 interfaces the CPU to the system bus (backplane) and drives toward the CPU during M1 or Read cycles. Buffers A26 and A23 drive the system address bus. A32 drives outbound control signals such as M1, IORQ, RD, etc., while A27 receives user provided inputs, e.g., INT, NMI, RESET, etc.

In actuality, system PHI is provided by the User Interface Module, which determines the appropriate development system clock. Zilog clock driver A25 provides a MOS compatible clock source for the LSI devices.

## 4.2.4 CONTROL BUFFER (Sheet 2)

Sheet 2 of the schematics detail the PROM/RAM implementation and the bus control logic for both A31 and A16 bus buffers.

Chip selects for Al7-Al9 and Al3, Al4 occur when PROM addresses are decoded by Sheet 3 logic. These decoded addresses, along with I/O and interrupt requests from peripherals A20 and A21 (Sheet 4) cause bus driver Al6 to drive the system data bus toward the CPU.

Automatic baud rate timing is acquired through tristate driver A28 and data bit D0, through Port FFH.

The Development System 3K Monitor is intended to provide the basic debugging commands, basic Input/Output driver firmware and bootstrap portion of a floppy disk-based operating system. The operation of this firmware is described in the ZDS-1/25, 1/40 PROM MANUAL.

## 4.2.5 DATA BUFFER (Sheet 3)

Sheet 3 depicts the address decoding assignments for the following:

PROM Firmware F000-FFFF HEX

Dynamic Memory 0-EFFF HEX

System Ports F0-FF HEX

Adder A34 translates monitor mode addresses from 00 to F000 placing memory select decoder A33 in the user address space (RAM at zero). Gates A7 and All generate the page 15 address enable which allows monitor mode PROM accesses. System I/O ports are decoded by the logic of A2 and A3.

## 4.2.6 ADDRESS BUFFER AND DECODER (Sheets 1, 2, and 4)

Sheet 4 contains the peripherals found on the CPU2 card. The console interface is implemented by way of USART A21, and CTC provides interrupt capability for the floppy disk interface and the USART status lines. Jumper El and E2 allow receiver interrupts from the USART. Flop flop A8 provides a square-wave baud-rate clock source to the USART.

Ī

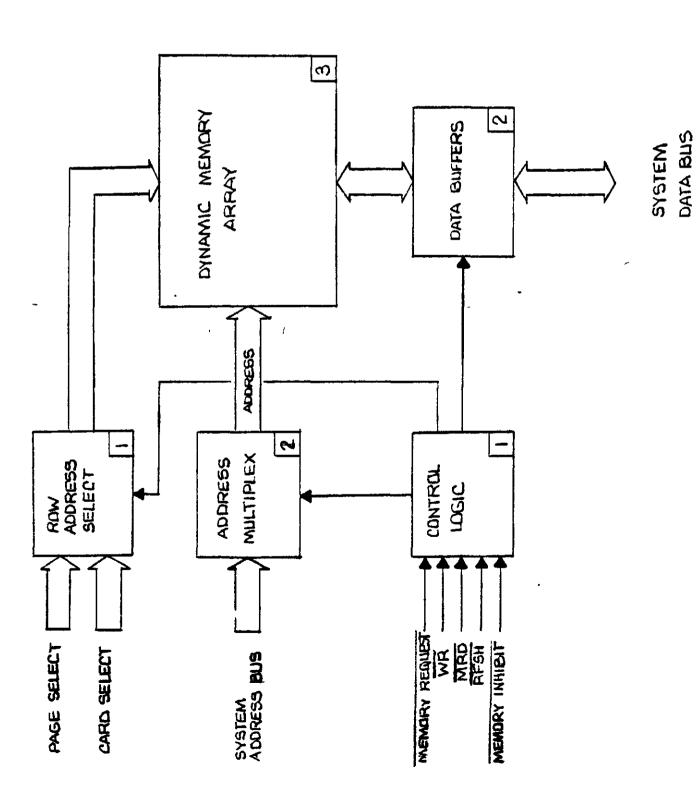

Figure 4-2 DYNAMIC MEMDRY MODULE

4.2.7 Z80-CTC (Counter Timer Circuit)

4.2.7.1 CTC Pin Description

D0-D7

Z80-CPU Data Bus (bi-directional, tri-state).

This bus is used to transfer all data and command words between the Z80-CPU and the Z80-CTC. There are 8 bits on this bus, of which D0 is the least significant.

CS1-CS0

Channel Select (input, active high)

These pins form a 2-bit binary address code for selecting one of the four independent CTC channels for an I/O write or read. (See truth table below.)

|     | CS1 | CS0 |

|-----|-----|-----|

| Ch0 | 0   | 0   |

| Chl | 0   | 1   |

| Ch2 | 1   | 0   |

| Ch3 | 1   | 1   |

CE-

Chip Enable (input, active low)

A low level on this pin enables the CTC to accept control words, interrupt vectors, or time constant data words from the Z80 data bus during an I/O write cycle, or to transmit the contents of the down counter to the CPU during an I/O ready cycle. In most applications, this signal is decoded from the 8 least significant bits of the address bus for any of the four I/O port addresses that are mapped to the four counter/timer channels.

Clock (phi)

System Clock (input)

This single-phase clock is used by the CTC to synchronize certain signals internally.

M1-

Machine Cycle One Signal from CPU (input, active low)

When M1- is active and the RD- signal is active, the CPU is fetching an instruction from memory. When M1- is active and the IORQ- signal is active, the CPU is acknowledging an interrupt, alerting the CTC to place an interrupt vector on the Z80 data bus if it has daisy chain priority and one of its channels has requested an interrupt.

IORQ-

Input/Output Request from CPU (input, active low)

The IORQ- signal is used in conjunction with the CE- and RD-signals to transfer data and channel control words between the Z80-CPU and the CTC. During a CTC write cycle, IORQ- and CE- must be true and RD- false. The CTC does not receive a specific write signal, instead generating its own internally from the inverse of a valid RD- signal. In a CTC read cycle, IORQ-, CE-, and RD- must be active to place the contents of the down counter on the Z80 data bus. If IORQ- and Ml- are both true, the CPU is acknowledging an interrupt request, and the highest-priority interrupting channel will place its interrupt vector on the Z80 data bus.

RD-

Read Cycle Status from the CPU (input, active low)

The RD- signal is used in conjunction with the IORQ- and CE-signals to transfer data and channel control words between the Z80-CPU and the CTC. During a CTC write cycle, IORQ- and CE- must be true and RD- false. The CTC does not receive a specific write signal, instead generating its own internally from the inverse of a valid RD- signal. In a CTC read cycle, IORQ-, CE-, and RD- must be active to place the contents of the down counter on the Z80 data bus.

IEI

Interrupt Enable In (input, active high)

This signal is used to help form a system-wide interrupt daisy chain which establishes priorities when more than one peripheral device in the system has interrupting capability. A high level on this pin indicates that no other interrupting devices of higher priority in the daisy chain are being

serviced by the Z80-CPU.

IEO

Interrupt Enable Out (output, active high)

The IEO signal, in conjunction with IEI, is used to form a system-wide interrupt priority daisy chain. IEO is high only if IEI is high and the CPU is not servicing an interrupt from any CTC channel. Thus, this signal blocks lower priority devices from interrupting while a higher priority interrupting device is being serviced by the CPU.

INT-

Interrupt Request (output, open drain, active low)

This signal goes true when any CTC channel which has been programmed to enable interrupts has a zero-count condition in its down counter.

RESET-

Reset (input, active low)

This signal stops all channels from counting and resets channel interrupt enable bits in all control registers, thereby disabling CTC-generated interrupts. The ZC/TO and INT- outputs go to their inactive states, IEO reflects IEI, and the CTC's data bus output drivers go to the high impedance state.

CLK/TRG3-CLK/TRG0

External Clock/Timer Trigger (input, user-selectable active high or low)

There are four CLK/TRG pins, corresponding to the four independent CTC channels. In the counter mode, every active edge on this pin decrements the down counter. In the timer mode, an active edge on this pin initiates the timing function. The user may select the active edge to be either rising or falling.

ZC/TO2-C/TO0

Zero Count/Timeout (output, active high)

There are three ZC/TO pins, corresponding to CTC channels 2

through 0. (Due to package pin limitations, channel 3 has no ZC/TO pin.) In either counter mode or timer mode, when the down counter decrements to zero, an active high going pulse appears at this pin.

# 4.2.7.2 CTC Programming

Before a Z80-CTC channel can begin counting or timing operations, a channel control word and a time constant data word must be written to it by the CPU. These words will be stored in the channel control register and the time constant register of that channel. In addition, if any of the four channels have been programmed with bit 7 of their channel control words to enable interrupts, an interrupt vector must be written to the appropriate register in the CTC. Due to automatic features in the interrupt control logic, one pre-programmed interrupt vector suffices for all four channels.

# Loading the Channel Control Register

To load a channel control word, the CPU performs a normal I/O write sequence to the port address corresponding to the CTC channel. Two CTC input pins, namely CSO and CS1, are used to form a 2-bit binary address to select one of four channels within the device. In many system architectures, these two input pins are connected to address bus lines AO and Al, respectively, so that the four channels in a CTC device will occupy contiguous I/O port addresses. A word written to a CTC channel will be interpreted as a channel control word, and loaded into the channel control register, with bit O being a logic 1. The other seven bits of this word select operating modes and conditions as indicated in the diagram below. Following the diagram, the meaning of each bit will be discussed in detail.

| D7                  | D6   | D5     | D4    | D3       | D2                       | Dl    | D0 |

|---------------------|------|--------|-------|----------|--------------------------|-------|----|

| Interrupt<br>Enable | Mode | Range* | Slope | Trigger* | Load<br>Time<br>Constant | Reset | 1  |

<sup>\*</sup> Used in timer mode only

#### Bit 7=1

The channel is enabled to generate an interrupt request sequence every time the down counter reaches a zero-count

condition. To set this bit to 1 in any of the four channel control registers necessitates that an interrupt vector also be written to the CTC before operation begins. Channel interrupts may be programmed in either counter mode or timer mode. If an updated channel control word is written to a channel already in operation with bit 7 set, the interrupt enable selection will not be retroactive to a preceding zero-count condition.

Bit 7=0

Channel interrupts disabled.

Bit 6=1

Counter mode selected. The down counter is decremented by each triggering edge of the external clock (CLK/TRG) input. The prescaler is not used.

Bit 6=0

Timer mode selected. The prescaler is clocked by the system clock , and the output of the prescaler in turn, clocks the down counter. The output of the down counter (the channel's ZC/TO output) is a uniform pulse train of periods given by the product

t \* P \* TC

where t is the period of system clock , P is the prescaler factor of 16 or 256, and TC is the time constant data word.

Bit 5=1

(Defined for timer mode only.) Prescaler factor is 256.

Bit 5=0

(Defined for timer mode only.) Prescaler factor is 16.

Bit 4=1

Timer mode - positive edge trigger starts timer operation. Counter mode - positive edge decrements the down counter.

Bit 4=0

Timer mode - negative edge trigger starts timer operation. Counter mode - negative edge decrements the down counter.

Bit 3=1

Timer mode only - external trigger is valid for starting timer operation after rising edge of T of the machine cycle following the one that loads the time constant. The prescaler is decremented two clock cycles later if the setup time is met, otherwise, three clock cycles.

Bit 3=0

Timer mode only - timer begins operation on the rising edge of T of the machine cycle following the one that loads the time constant.

Bit 2=1

The time constant data word for the time constant register will be the next word written to this channel. If an updated channel control word and time constant data word are written to a channel while it is already in operation, the down counter will continue decrementing to zero before the new time constant is loaded into it.

Bit 2=0

No time constant data word for the time constant register should be expected to follow. To program bit 2 to this state implies that this channel control word is intended to update the status of a channel already in operation, since a channel will not operate without a correctly programmed data word in the time constant register, and a set bit 2 in this channel control word provides the only way of writing to the time constant register.

Bit 1=1

Reset channel. Channel stops counting or timing. This is not a stored condition. Upon writing into this bit, a reset pulse discontinues current channel operation, however, none of the bits in the channel control register are changed. If both bit 2=1 and bit 1=1, the channel will resume operation upon loading a time constant.

Bit 1=0

Channel continues current operation.

A channel may not begin operation in either timer mode or counter mode unless a time constant data word is written into

the time constant register by the CPU. This data word will be expected on the next I/O write to this channel following the I/O write of the channel control word, provided bit 2 of the channel control word is set. The time constant data word may be any integer value in the range 1-256. If all eight bits in this word are zero, it is interpreted as 256. If a time constant data word is loaded to a channel already in operation, the down counter will continue decrementing to zero before the new time constant is loaded from the time constant register to the down counter.

Time Constant Register

| D7  | D6  | D5  | D4  | D3  | D2  | Dl  | D0  |

|-----|-----|-----|-----|-----|-----|-----|-----|

| TC7 | TC6 | TC5 | TC4 | TC3 | TC2 | TC2 | TCO |

MSB

The Z80-CTC has been designed to operate with the Z80-CPU programmed for mode 2 interrupt response. Under the requirements of this mode, when a CTC channel requests an interrupt and is acknowledged, a 16-bit pointer must be formed to obtain a corresponding interrupt service routine starting address from a table in memory. The upper 8 bits of this pointer are provided by the CPU's I register, and the lower 8 bits of the pointer are provided by the CTC in the form of an interrupt vector unique to the particular channel that requested the interrupt.

MODE 2 INTERRUPT OPERATION

INTERRUPT

SERVICE

ROUTINE

STARTING

ADDRESS

TABLE

Desired starting address

pointed to by:

I REG 7 BITS FROM 0

CONTENTS PERIPHERAL

The high order 5 bits of this interrupt vector must be written to the CTC in advance as part of the initial programming sequence. To do so, the CPU must write to the I/O port addresses corresponding to the CTC channel 0, just as it would if a channel control word were being written to that channel, except that bit 3 of the word being written must contain a 0. (As explained above in Section 3.1, if bit 0 of a word written to a channel were set to 2, the word would be interpreted as a channel control word, so a 0 in bit

O signals the CTC to load the incoming word into the interrupt vector register.) Bits 1 and 2, however, are not used when loading this vector. At the time when the interrupting channel must place the interrupt vector on the Z80 data bus, the interrupt control logic of the CTC automatically supplies a binary code in bits 1 and 2 identifying which of the four CTC channels is to be serviced.

### Channel 2 - Baud Rate Generation

This channel may be operated in either counter or timer mode and is triggered or clocked by the output of A4-pin 9. Once the counter decrements to zero, the ZC2 output goes active (high) to clock the second stage of A4 whose output provides the transmit and receive clocks to the USART.

# Channel 3 - USART Transmit Interrupt Generator

This channel allows the USART to have interrupt capability with the system. This channel will generate an interrupt upon receiving a TxRDY signal from the USART.

# 4.2.8 USART Operation

# 4.2.8.1 USART Signal Description

Data Bus (D0-D7)

This tree-state, 8-bit bus is used for information exchange between the USART and the host processor. Data, controk, andd stat6us bytes are exchanged upon execution of input and output instructions from the Z80.

### Reset (RST)

The USART will assume an idle sstate when a high level is applied to the reset input. When the reset is returned low, the USART will remain in the idle state until it receives a new mode control instruction.

### Clock (CLK)

This input is used for internal timing within the USART. It does not control the transmit or rec3eive rate. However, it should be at least 30 times the reeceive or transmit rate in the synchronous mode and 4.5 times the receive or transmit rates in the asynchronous mode. The CLK frequency is also restricted by both an upper and a lower bound.

### INTERRUPT VECTOR REGISTER

| D7 | D6               | D5 | D4 | D3 | D2   | Dl   | D0                           |

|----|------------------|----|----|----|------|------|------------------------------|

| V7 | V6               | V5 | V4 | V3 | /x// | //x/ |                              |

| Su | Supplied by User |    |    |    | 0    | 0    | Channel 0 (highest priority) |

|    |                  |    |    |    | 0    | 1    | Channel 1                    |

|    |                  |    |    |    | 1    | 0    | Channel 2                    |

|    |                  |    |    |    | 1    | 1    | Channel 3                    |

|    |                  |    |    |    |      |      | (lowest priority)            |

|    |                  |    |    |    | Auto |      | cally inserted<br>v Z80-CTC  |

### 4.2.8.2 CTC Utilization

All four channels of the Z80-CTC are used by the system for various timing functions. The channels used and their purpose are shown below:

### Channel 0 - Sector Counter

This channel is operated in counter mode and is used as a Sector Counter for the Floppy Disk Controller. Interrupts are used with this channel to flag software as to when the appropriate number of sector pulses have been received from the disk so that the heads may be loaded. This counter is incremented by the signal, INDX, from the Flopppy Disk Controller Module.

#### Channel 1 - Bit Measurement

This channel is operated in timer mode and is triggered by the RCUR OUT signal from the Serial Latches on the CPU module. The output of the channel (ZCl) becomes RCV CLK which is routed to the CPU module to clock the RCVR OUT signal into the Serial Latches.

# Control/Data (C/D)

During a read operation, if this input is at a high level, the status byte will be read, and if it is at a lcw level, the receive data will be read by the processor. When a write operation is being performed, this input will indicate to the USART that the bus information being written is a command if

C/D is high and data if C/D is low.

| C/D- | RD- | WR- | CS- |                        |

|------|-----|-----|-----|------------------------|

| 0    | 0   | 1   | 0   | USART DATA>DATA BUS    |

| 0    | 1   | 0   | 0   | DATA BUS>USART DATA    |

| 1    | 0   | 1   | 0   | USART STATUS>DATA BUS  |

| 1    | 1   | 0   | 0   | DATA BUS>USART COMMAND |

| X    | X   | X   | 1   | DATA BUS>3-STATE       |

Read (RD-)

This active low input enables data or status to be transferred from the USART to the Z80.

Write (WR-)

This active low input enables data or control to be transferred to the USART from the 280.

Chip Select (CS-)

This active low input enables the processor to access the USART for an I/O operation. When CS- is high, the data bus output is in the high impedance state.

Data Set Ready (DSR-)

This is a general-purpose input signal and forms part of the status byte that may be read by the processor. DSR- is generally used as a response to DTR by the modem to indicate that it is ready. The signal acts only as a flag and does not control any internal logic.

Data Terminal Ready (DTR-)

This output signal reflects the condition of bit 1 in the command byte from the Z80. The DTR signal is commonly used for data terminal ready or rate select in modem control.

Clear to Send (CTS-)

This is a general-purpose input signal used to enable the USART to transmit data if the TxEN bit in the command byte is a one. CTS- is generally used as a response to RTS- by a modem to indicate that transmission may begin. Designers not using CTS- in their systems should remember to tie it low so that USART data transmission will not be disabled.

Request to Send (RTS-)

This output signal reflects the condition of bit 5 in the command byte from the Z80. The RTS- signal is commonly used to initiate a data transmission by requesting the modem to prepare to send.

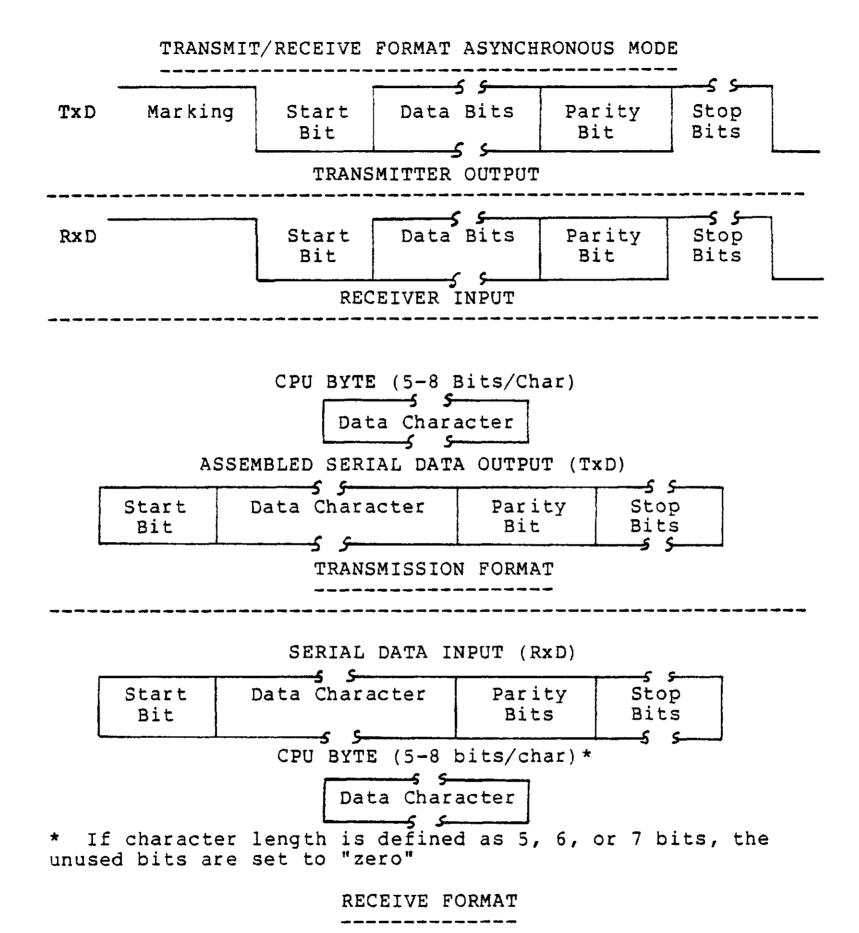

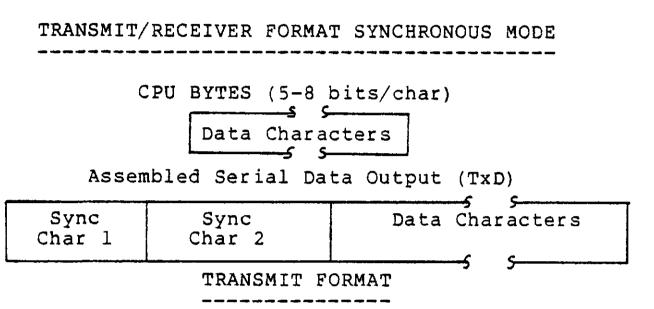

Transmit Data (TxD)

Data from the data bus is converted to a serial format with appropriate sync, start/stop, and parity information inserted into the data stream. This bit stream is then transmitted to the TxD output.

Transmitter Ready (TR)

The TR output signal goes high when data in the transmit data buffer has been shifted into the transmitter section allowing the transmit data buffer to accept the next byte from the processor. TR will be reset when information is written into the transmit data buffer. Loading the command register also resets TR. TR will be available on this output pin only when the USART is enabled to transmit (CTS-=0, TxEN=1). However, the TxRDY bit in the status buffer will always be set when the transmit data buffer is empty regardless of the state of TxEN and CTS-.

TR can be tested by checking bit 0 of the status register for polling operation or the TR signal can be used to generate an interrupt. On the SCON, CTC2 is used to receive the active high TR signal from the USART to decrement a counter from 1 to 0, and consequently, provide a Z80 mode 2 interrupt vector.

Transmitter Clock (TxC-)

The transmitter clock controls the serial character transmission rate. In the asynchronous mode, the TxC- frequency is a multiple of the actual baud rate. Bits 0 and 1 of the mode instruction select the multiple to be lx, l6x, or 64x the baud rate. In the synchronous mode, the TxC- frequency is automatically selected to equal the actual baud rate.

Note that for both synchronous and asynchronous modes, serial data is shifted out of the USART by the falling edge of TxC-.

Receive Data (RxD)

Composite serial data is received at this input and converted

to a parallel format; sync, start/stop, and parity are checked, and then the assembled byte is prepared for buffering to the Z80. For communications requiring less than 8 bits per character, the extra bits are set to logical "zero".

### Receiver Ready (RR)

The RR output signal indicates to the processor that data has been shifted into the receiver buffer from the receiver section and may be read. The signal is active high and will be reset when the buffer is read by the processor. RR can be activated only if the receiver enable (RxE) has been set in the command register, even though the receiver may be running. If the processor does not read the receiver buffer before the next character is shifted from the receiver section, then an overrun error will be indicated in the status buffer.

RR can be tested by checking bit 1 of the status register for polling operation or the RR signal can be used to generate an interrupt. On the SCON, CT1 may be used to receive the active high RR signal from the USART to decrement a counter from 1 to 0, and consequently, provide a Z80 mode 2 interrupt vector.

# Receiver Clock (RxC-)

The receiver clock is the rate at which the incoming character is received. In the asynchronous mode, the RxC frequency may be 1, 16, or 64 times the actual baud rate, but in the synchronous mode, the RxC- frequency must equal the baud rate. Bits 0 and 1 in the mode instruction select asynchronous at 1x, 16x, or 64x or synchronous operation at 1x the baud rate.

Unlike TxC-, data is sampled by the USART on the rising edge of RxC-. Since the USART will frequently be handling both the reception and transmission for a given link, the receive and transmit baud rates will be the same. RxC- and TxC- then require the same frequency and may be tied together and connected to a single clock source or baud rate generator.

#### Sync Detect (SYNC)

This signal is used only in the synchronous mode. It can be an input or output depending on the USART mode instruction, programming the operation for external or internal synchronization, respectively. In the internal sync mode, the SYNC "output" will go to a logical one when the USART has

identified the sync character in the receiver data stream. If the USART is programmed for "bi-sync" operation, the sync output will not go to a logical one until the second consecutive sync character has been identified. In both cases, the sync output transition from low to high will occur in the middle of the last bit of the respective sync character. Sync and bit 6 (sync) in the status register are reset when the status buffer is read or when a device RST occurs.

In the external sync mode, a positive edge on the sync "input" will cause the USART to start assembling a data byte on the next falling edge of RxC-. The sync signal should remain high for at least one RxC- period.

# 4.2.8.3 USART Operation

A set of control words must be sent to the USART to define the desired mode and communications format. The control words will specify the baud rate factor (lx, l6x, 64x), character length (5 to 8), number of stop bits (l, 3/2, 2), asynchronous or synchronous mode, syndet (internal or external), parity, etc.

After receiving the control words, the USART is ready to communicate. TxRDY is raised to signal the processor that the USART is ready to receive a character for transmission. When the processor writes a character to the USART, TxRDY is automatically reset.

Concurrently, the USART may receive serial data; and after receiving an entire character, the RxRDY output is raised to indicate a completed character is ready for the processor. The processor fetch will automatically reset RxRDY.

NOTE: The 8251 and 9551 USARTs may provide faulty data from the receiver buffer for the first read after power-on. A dummy read is recommended.

The USART cannot transmit until the TxEN (Transmitter Enable) bit has been set by a command instruction and until the CTS-(Clear to Send) input is a "zero".

#### 4.2.8.4 USART Programming

The USART must be loaded with a group of two to four control words provided by the processor before data reception and transmission can begin. A reset (internal or external) must immediately proceed the control words which are used to program the complete operational description of the

communications interface. If an external reset is not available, three successive zeros followed by a reset command instruction can be used to initialize the USART. TxD is held in the "marking" state after reset, waiting for a new command instruction.

There are two control word formats:

- 1. Mode Instruction

- 2. Command Instruction

#### Mode Instruction

This control word specifies the general characteristics of the interface regarding the synchronous or asynchronous mode, baud rate factor, character length, parity, and number of stop bits. Once the mode instruction has been received, sync characters or command instructions may be inserted depending on the mode instruction content.

#### Command Instruction

This control word directs the actual operation of the format selected in the mode instruction. Functional control of transmit and receive, error reset, reset, and modem signals are accommodated in the command instruction.

# ASYNCHRONOUS OPERATION

# SYNCHRONOUS OPERATION

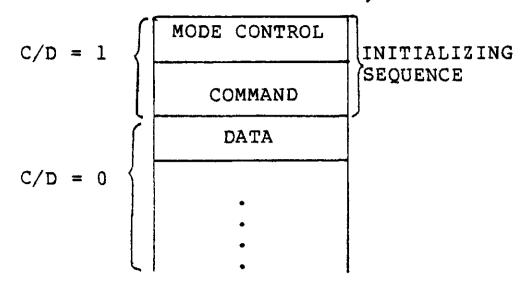

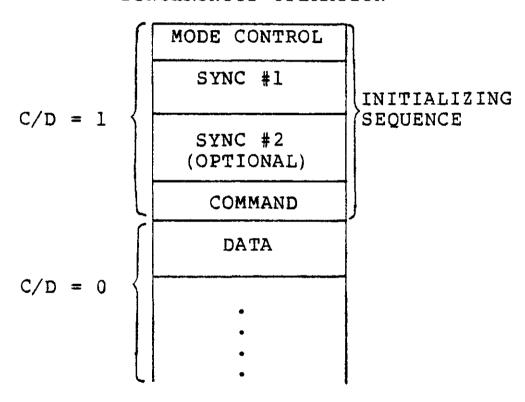

FIGURE 4-13: Control Word Sequence for Initialization

Only a single address is set aside for mode control bytes, command bytes, and sync character bytes. For this to be possible, logic internal to the chip directs control information to its proper destination based on the sequence in which it is received. Following a reset, the first control code output is interpreted as a mode control. If the mode control specifies synchronous operation, then the next one or two bytes (as determined by the mode byte) output as control codes will be interpreted as sync characters. For either asynchronous or synchronous operation, the next byte output as a control code is interpreted as a command. All subsequent bytes output as control codes are interpreted as commands. There are two ways in which control logic may return to anticipating a mode control input; following an external reset signal or following an internal reset command.

### Mode Control Codes

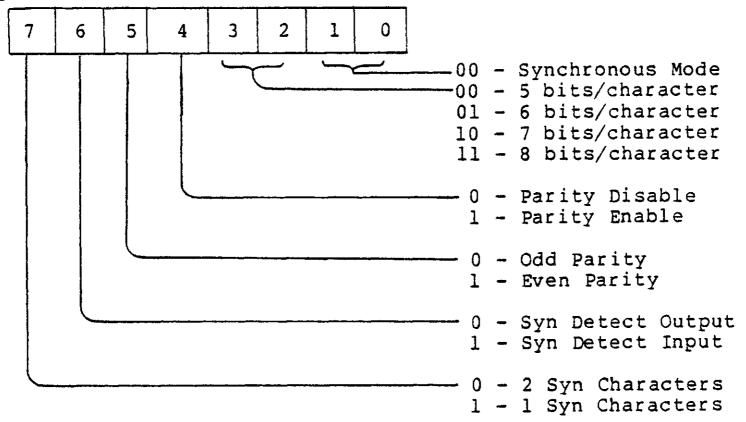

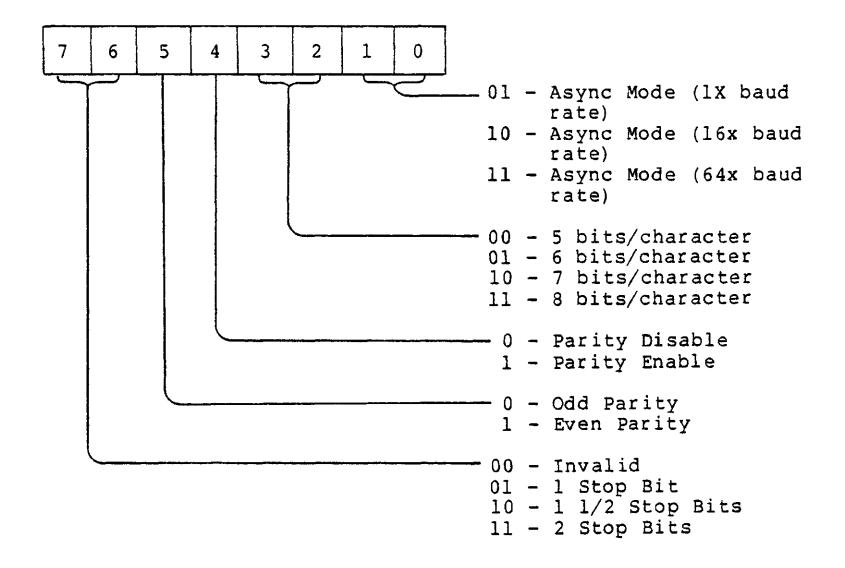

The USART interprets mode control codes as illustrated in Figures 4-14 and 4-15.

Control code bits 0 and 1 determine whether synchronous or asynchronous operation is specified. A non-zero value in bits 0 and 1 specifies asynchronous operation and defines the relationship between the data transfer baud rate and receiver or transmitter clock rate. Asynchronous serial data may be received or transmitted on every clock pulse, on every 16th clock pulse, or on every 64th clock pulse. A zero in both bits 0 and 1 defines the mode of operation as synchronous.

For synchronous and asynchronous modes, control bits 2 and 3 determine the number of data bits which will be present in each data character.

For synchronous and asynchronous modes, bits 4 and 5 determine whether there will be a parity bit in each character, and if so, whether odd or even parity will be adopted. Thus, in synchronous mode, a character will consist of five, six, seven, or eight data bits, plus an optional parity bit. In asynchronous mode, the data unit will consist of five, six, seven, or eight data bits, an optional parity bit, a preceeding start bit, plus 1, 1 1/2, or 2 trailing stop bits. Interpretation of subsequent bits differs for synchronous or asynchronous modes.

Control code bits 6 and 7 in asynchronous mode determine how many stop bits will trail each data unit. 1 1/2 stop bits can only be specified with a 16x or 64x baud rate factor. In these two cases, the half stop bit will be equivalent to 8 or 32 clock pulses, respectively.

In synchronous mode, control bits 6 and 7 determine how character synchronization will be achieved. When syndet is an output, internal synchronization is specified; one or two sync characters, as specified by control bit 7, must be detected at the head of a data stream in order to establish synchronization.

Figure 4-14. Synchronous Mode Control Codes

#### Mode Instruction Definition

The USART can operate in either asynchronous or synchronous communication modes. Understanding how the mode instruction controls the functional operation of the USART is easiest when the device is considered to be two separate components, one asynchronous and the other synchronous, which share the same support circuits and package. Although the format definition can be changed at will or "on the fly", the two modes will be explained separately for clarity.

Figure 4-15. Asynchronous Mode Control Code

### Asynchronous Mode

When a data character is written into the USART, it automatically adds a start bit (low level or "space") and the number of stop bits (high level or "mark") specified by the mode instruction. If parity has been enabled, an odd or even parity bit is inserted just before the stop bit(s), as specified by the mode instruction. Then, if CTS- and TxEN are active, the character is transmitted as a serial data stream at the TxD output. Data is shifted out by the falling edge of TxC- at TxC-, TxC/16- or TxC-/64, as defined by the mode instruction.

If no data characters have been loaded into the USART, or if all available characters have been transmitted, the TxD output remains "high" (marking) in preparation for sending the start bit of the next character provided by the processor. TxD may be forced to send a break (continuously low) by setting the correct bit in the command instruction.

The RxD input line is normally held "high" (marking) by the transmitting device. A falling edge at RxD signals the possible beginning of a start bit and a new character. The start bit is checked by testing for a "low" at its nominal center and the bit assembling counter starts counting. bit counter locates the approximate center of the data, parity (if specified), and stop bits. The parity error flag (PE) is set, if a parity error occurs. Input bits are sampled at the RxD pin with the rising edge of RxC-. If a high is not detected for the stop bit, which normally signals the end of an input character, a framing error (FE) will be After a valid stop bit, the input character is loaded into the parallel data bus buffer of the USART and the RxRDY signal is raised to indicate to the processor that a character is ready to be fetched. If the processor has failed to fetch the previous character, the new character replaces the old and the overrun flag (OE) is set. All the error flags can be reset by setting a bit in the command instruction. Error flag conditions will not stop subsequent USART operation.

# Synchronous Transmission

As in asynchronous transmission, the TxD output remains "high" (marking) until the uPD8251 receives the first character from the processor which is usually a sync character. After a command instruction has set TxEN and after clear to send (CTS-) goes low, the first character is serially transmitted. Data is shifted out on the falling edge of TxC- and the same rate as TxC-.

Once transmission has started, synchonronus mode format requires that the serial data stream at TxD continue at the TxC- rate or sync will be lost. If a data character is not provided by the processor before the uPD8251 transmitter buffer becomes empty, the sync character(s) loaded directly following the mode instruction will be automatically inserted in the TxD data stream. The sync character(s) are inserted to fill the line and maintain synchronization until new data characters are available for transmission. If the USART becomes empty, and must send the sync character(s), the TxEMPTY output is raised to signal the processor that the transmitter buffer is empty and sync characters are being transmitted. TxEMPTY is automatically reset by the next character from the processor.

### Synchronous Receive

In synchronous receive, character synchronization can be either external or internal. If the internal sync mode has been selected, and the enable hunt (EH) bit has been set by a command instruction, the receiver goes into the hunt mode.

Incoming data on the RxD input is sampled on the rising edge of RxC-, and the receiver buffer is compared with the first sync character after each bit has been loaded until a match is found. If two sync characters have been programmed, the next received character is also compared. When the sync character(s) programmed have been detected, the USART leaves the hunt mode and is in character synchronization. At this time, the syndet (output) is set high. Syndet is automatically reset by a status read.

If external sync has been specified in the mode instruction, a "one" applied to the syndet (input) for at least one RxC-cycle will synchronize the USART.

Parity and overrun errors are treated the same in the synchronous as in the asynchronous mode. Framing errors do not apply in the synchronous format.

The processor may command the receiver to enter the hunt mode with a command instruction which sets enable hunt (EH) if synchronization is lost.

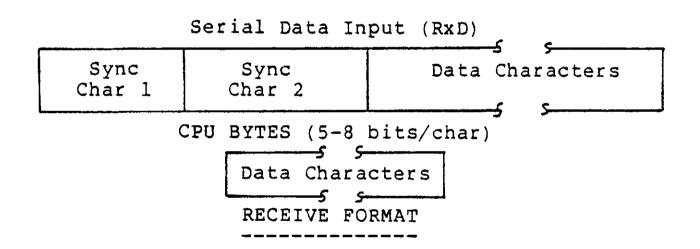

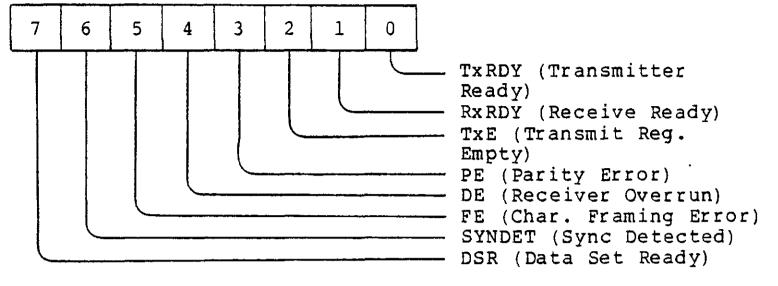

#### Command Words

Command words are used to initiate specific functions within the USART, such as, "reset all error flags" or "start searching for sync". Consequently, command words may be issued by the microprocessor to the USART at any time during the execution of a program in which specific functions are to be initiated within the communication circuit.

A reset operation (internal via CMD IR or external via the reset input) will cause the USART to interpret the next "control write", which must immediately follow the reset, as a mode instruction. Following the mode instruction, a command word, of the format shown in Figure 4-16, is issued

to the USART.

Figure 4-16. USART Control Command

Bit 0 of the command word is the transmit enable bit (TxEN). Data transmission from the USART cannot take place unless TxEN is set in the command register. Figure 5 defines the way in which TxEN, TxE, and TxRDY combine to control transmitter operations.

Bit I is the data terminal ready (DTR) bit. When the DTR command bit is set, the DTR- output connection is active (low). DTR is used to advise a modem that the data terminal is prepared to accept or transmit data.

Bit 2 is the receiver enable command bit (RxE). RxE is used to enable the RxRDY output signal. RxE prevents the RxRDY signal from being generated to notify the processor that a complete character is framed in the receive character buffer. It does not inhibit the assembly of data characters at the input, however. Consequently, if communication circuits are active, characters will be assembled by the receiver and

transferred to the receiver character buffer. If RxE is disabled, the overrun error (OE) will probably be set; to insure proper operation, the overrun error is usually reset with the same command that enables RxE.

Table 4-2. Transmitter Section Operation

| TXEN | TxE | Tx RDY |                                                                                                                                                                                                                            |

|------|-----|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | 1   | 1      | Transmit output register and transmit character buffer empty. TxD continues to mark if USART is in the asynchronous mode. TxD will send sync pattern if USART is in the synchronous mode. Data can be entered into buffer. |

| 1    | 0   | 1      | Transmit output register is shifting a character. Transmit character buffer is available to receive a new byte from the processor.                                                                                         |

| 1    | 1   | 0      | Transmit register has finished sending. A new character is waiting for transmission. This is a transient condition.                                                                                                        |

| 1    | 0   | 0      | Transmit register is currently sending and an additional character is stored in the transmit character buffer for transmission.                                                                                            |

| 0    | X   | X      | Transmitter is disabled.                                                                                                                                                                                                   |

Bit 3 is the send break command bit (SBRK). When SBRK is set, the transmitter ouput (TxD) is interrupted and a continuous binary "0" level (spacing), is applied to the TxD output signal. The break will continue until a subsequent command word is sent to the USART to remove SBRK.

Bit 4 is the error reset bit (ER). When a command word is

transmitted with the ER bit set, all three error flags in the status register are reset. Error reset occurs when the command word is loaded into the USART. No latch is provided in the command register to save the ER command bit.

Bit 5, the request to send command bit (RTS), sets a latch to reflect the RTS signal level. The output of this latch is created independently of other signals in the USART. As a result, data transfers may be made by the microprocessor to the transmit register, and data may be actively transmitted to the communication line through TxD regardless of the status of RTS.

Bit 6, the internal reset (IR), causes the USART to return to the idle mode. All functions within the USART cease, and no new operation can be resumed until the circuit is reinitiallized. If the operating mode is to be altered during the execution of a microprocessor program, the USART must first be reset. Either the external reset connection can be activated, or the internal reset command can be sent to the USART. Internal reset is a momentary function performed only when the command is used.

Bit 7 is the enter hunt command bit (EH). The enter hunt mode command is only effective for the USART when it is operating in the synchronous mode. EH causes the receiver to stop assembling characters at the RxD input and start searching for the prescribed sync pattern. Once the "enter hunt" mode has been initiated, the search for the sync pattern will continue indefinitely until EH is reset when a subsequent command word is sent, when the IR command is sent to the USART, or when sync characters are recognized.

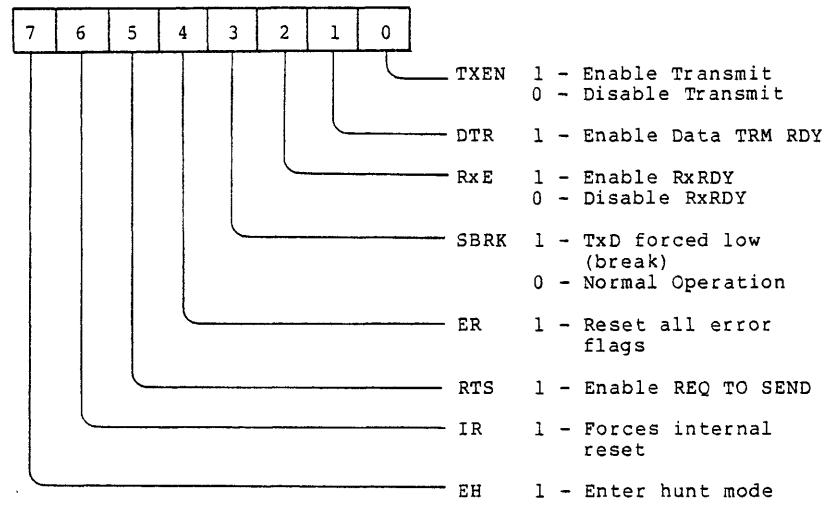

### Status Read Format

It is frequently necessary for the processor to examine the "status" of an active interface device to determine if errors have occurred or to notice other conditions which require a response from the processor. The USART has features which allow the processor to "read" the device status at any time. A data fetch is issued by the processor while holding the C/D- input "high" to obtain device status information. Many of the bits in the status register are copies of external pins. This dual status arrangement allows the USART to be used in both polled and interrupt driven environments.

TxRDY signals the processor that the transmit character buffer is empty and that the USART can accept a new character for transmission.

RxRDY signals the processor that a completed character is holding in the receive character buffer register for transfer to the processor.

TxE signals the processor that the transmit register is empty.

PE is the parity error signal indicating to the CPU that the character stored in the receive character buffer was received with an incorrect number of binary "l" bits. The PE flag is cleared by setting the ER bit in a subsequent command instruction. PE being set does not inhibit USART operation.

OE is the receiver overrun error. OE is set whenever a byte stored in the receiver character register is overwritten with a new byte before being transferred to the processor. The OE flag is cleared by setting the ER bit in a subsequent command instruction. OE being set does not inhibit USART operation.

FE is the character framing error which indicates that the asynchronous mode byte stored in the receiver character buffer was received with an incorrect character bit format (stop bit), as specified by the current mode. The FE flag is cleared by setting the ER bit in a subsequent command instruction. FE being set does not inhibit USART operation.

#### 4.3 DYNAMIC MEMORY MODULE